Waarom en hoe Efinix FPGA's gebruiken voor AI/ML-beeldvorming Deel 2: Beeldopname en -verwerking

Bijgedragen door De Europese redacteurs van DigiKey

2023-05-05

Noot van de redactie: Nieuwe benaderingen van FPGA-architecturen zorgen voor een fijnmaziger controle en meer flexibiliteit om tegemoet te komen aan de behoeften van machine learning (ML) en kunstmatige intelligentie (AI). Deel 1 van deze tweedelige serie introduceert een dergelijke architectuur van Efinix en hoe ermee aan de slag te gaan met behulp van een ontwikkelbord. In deel 2 wordt ingegaan op de koppeling van het ontwikkelingsbord met externe apparaten en randapparatuur, zoals een camera, en hoe de FPGA kan worden gebruikt om knelpunten in de beeldverwerking weg te nemen.

FPGA's spelen een cruciale rol in vele toepassingen, van industriële besturing en veiligheid tot robotica, ruimtevaart en automobielindustrie. Dankzij het flexibele karakter van de programmeerbare logicakern en hun brede interfacemogelijkheden is een groeiend gebruik van FPGA's in de beeldverwerking, waar machine learning (ML) kan worden toegepast. Dankzij hun parallelle logische structuur zijn FPGA's ideaal voor de implementatie van oplossingen met meerdere snelle camera-interfaces. Bovendien maken FPGA's ook het gebruik van een specifieke verwerkingspijplijn in de logica mogelijk, waardoor knelpunten met gedeelde middelen, zoals bij CPU- of GPU-gebaseerde oplossingen, worden weggenomen.

In deze tweede blik op de Titanium FPGA's van Efinix wordt de referentie-beeldverwerkingsapplicatie onderzocht die wordt geleverd met de Ti180 M484-ontwikkelingskaart van de FPGA. Het doel is de samenstellende delen van het ontwerp te begrijpen en na te gaan waar de FPGA-technologie het mogelijk maakt knelpunten op te heffen of andere voordelen voor de ontwikkelaars mogelijk maakt.

Het op Ti180 M484 gebaseerde referentieontwerp

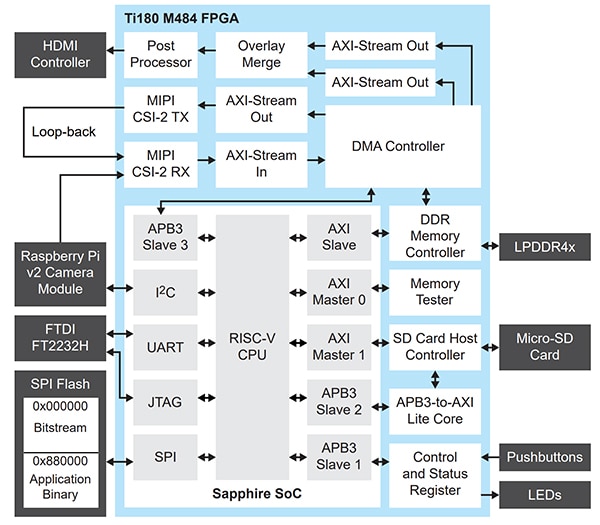

Conceptueel gezien ontvangt het referentieontwerp (figuur 1) beelden van verschillende Mobile Industry Processor Interface (MIPI) camera's, voert frame-buffering uit in de LPDDR4x, en voert vervolgens de beelden uit naar een High Definition Multimedia Interface (HDMI) display. Een FPGA Mezzanine Card (FMC) en vier Samtec QSE-interfaces op het bord worden gebruikt om de camera-ingangen en de HDMI-uitgang te leveren.

Afbeelding 1: Conceptueel ontvangt het Ti180 M484-referentieontwerp beelden van verschillende MIPI-camera's, voert framebuffering uit in de LPDDR4x, en voert vervolgens de beelden uit naar een HDMI-scherm. >(Bron afbeelding: Efinix)

Afbeelding 1: Conceptueel ontvangt het Ti180 M484-referentieontwerp beelden van verschillende MIPI-camera's, voert framebuffering uit in de LPDDR4x, en voert vervolgens de beelden uit naar een HDMI-scherm. >(Bron afbeelding: Efinix)

De FMC naar QSE-uitbreidingskaart wordt gebruikt in combinatie met de HDMI-dochterkaart om het uitgaande videopad te leveren, terwijl drie QSE-connectoren worden gebruikt voor de interface met de DFRobot SEN0494 MIPI-camera's. Als er geen meerdere MIPI-camera's beschikbaar zijn, kan één camera worden gebruikt door het kanaal van de enkele camera terug te lussen om extra camera's te simuleren.

Op een hoog niveau lijkt deze toepassing eenvoudig. Het ontvangen van meerdere high-definition (HD) MIPI-streams met een hoge beeldsnelheid is echter een uitdaging. Dit is waar FPGA-technologie voordelig is, omdat ontwerpers hiermee meerdere MIPI-streams parallel kunnen gebruiken.

De architectuur van het referentieontwerp maakt gebruik van zowel parallelle als sequentiële verwerkingsstructuren met de FPGA. De parallelle structuren worden gebruikt voor de uitvoering van de beeldverwerkingspijplijn, terwijl een RISC-V-processor zorgt voor de sequentiële verwerking die wordt gebruikt voor de FPGA-look-up tables (LUTs).

De beeldverwerkingspijplijn kan in veel op FPGA gebaseerde beeldverwerkingssystemen worden opgesplitst in twee elementen, namelijk de input- en outputstreams. De inputstream wordt verbonden met de camera/sensor-interface, en verwerkingsfuncties worden toegepast op de uitvoer van de sensor. Deze functies kunnen bestaan uit Bayer-conversie, automatische witbalans en andere verbeteringen. In de outputstream wordt het beeld voorbereid voor weergave. Dit omvat het wijzigen van kleurruimten (bijv. RGB naar YUV) en nabewerking voor het gewenste uitvoerformaat, zoals HDMI.

Vaak werkt de beeldverwerkingsketen aan de pixelkloksnelheid van de sensor. Deze heeft een andere timing dan de uitgangsketen, die wordt verwerkt op de frequentie van de uitgangsweergave.

Een framebuffer wordt gebruikt om de invoer te verbinden met de uitvoerverwerkingspijplijn, die vaak wordt opgeslagen in extern krachtig geheugen, zoals LPDDR4x. Deze framebuffer is ontkoppeld tussen de invoer- en uitvoerleidingen, zodat toegang tot de framebuffer mogelijk is via directe geheugentoegang op de juiste klokfrequentie.

Het Ti180-referentieontwerp gebruikt een soortgelijke aanpak als de hierboven geschetste concepten. De invoerbeeldverwerkingspijplijn implementeert een MIPI Camera Serial Interface 2 (CSI-2) ontvanger intellectuele eigendom (IP) kern, die is gebouwd op de MIPI fysieke laag (MIPI D-PHY)-capabele input/output (I/O) van de Titanium FPGA. MIPI is een uitdagende interface omdat deze zowel single-ended als differentiële signalering op hetzelfde differentiële paar gebruikt, naast communicatie op lage snelheid en op hoge snelheid. De integratie van de MIPI D-PHY in de FPGA I/O vermindert de complexiteit van het ontwerp van de circuitkaart en vermindert tevens de stuklijst (BOM).

Met de imagestream van de camera ontvangen, zet het referentieontwerp vervolgens de uitvoer van de MIPI CSI-2 RX om in een Advanced eXtensible Interface (AXI) Stream. Een AXI Stream is een unidirectionele snelle interface die een gegevensstream van een master naar een slave levert. Er zijn handshakingssignalen voor de overdracht tussen een master en slave (tvalid en tready) en sidebandsignalen. Deze zijbandsignalen kunnen worden gebruikt om beeldtijdinformatie over te brengen, zoals het begin van het frame en het einde van de regel.

AXI Stream is ideaal voor beeldverwerkingstoepassingen en stelt Efinix in staat een reeks beeldverwerkings-IP te leveren die vervolgens eenvoudig in de verwerkingsketen kan worden geïntegreerd zoals vereist door de toepassing.

Na ontvangst worden de MIPI CSI-2 beeldgegevens en timingsignalen omgezet in een AXI Stream en ingevoerd in een DMA-module (Direct Memory Access), die het beeldkader naar de LPDDR4x schrijft en als kaderbuffer fungeert.

Deze DMA-module werkt onder controle van de RISC-V-kern in de FPGA binnen een Sapphire-systeem op chip (SoC). Deze SoC biedt controle, zoals het stoppen en starten van DMA-schrijvingen, naast het voorzien van het DMA-schrijfkanaal van de nodige informatie om de beeldgegevens correct naar de LPDDR4x te schrijven. Dit omvat informatie over de geheugenplaats en de breedte en hoogte van de afbeelding, gedefinieerd in bytes.

Het uitgangskanaal in het referentieontwerp leest de beeldinformatie uit de LPDDR4x-framebuffer onder besturing van de RISC-V SoC. De gegevens worden door de DMA IP uitgevoerd als een AXI Stream, die vervolgens van het RAW-formaat van de sensor wordt omgezet in RGB-formaat (Afbeelding 2), en voorbereid voor uitvoer via de ingebouwde HDMI-zender ADV7511 van Analog Devices.

Afbeelding 2: Voorbeeldbeelden van het referentieontwerp. (Bron afbeelding: Adam Taylor)

Afbeelding 2: Voorbeeldbeelden van het referentieontwerp. (Bron afbeelding: Adam Taylor)

Door het gebruik van de DMA heeft de Sapphire SoC RISC-V ook toegang tot de beelden die in de framebuffer zijn opgeslagen, en tot de abstracte statistieken en beeldinformatie. De Sapphire SoC kan ook overlays schrijven in de LPDDR4x, zodat deze kunnen worden samengevoegd met de uitgaande videostream.

Moderne CMOS-beeldsensoren (CIS's) hebben verschillende werkingsmodi en kunnen worden geconfigureerd voor verwerking op de chip en verschillende uitvoerformaten en klokschema's. Deze configuratie geschiedt normaliter via een I²C-interface. In het Efinix-referentieontwerp wordt deze I²C-communicatie naar de MIPI-camera's verzorgd door de Sapphire SoC RISC-V-processor.

De integratie van de RISC-V-processor in de Titanium FPGA vermindert de totale omvang van de uiteindelijke oplossing, omdat er geen complexe FPGA-statusmachines meer nodig zijn die het ontwerprisico vergroten, en ook geen externe processoren die de BOM verhogen.

De opname van de processor maakt ook ondersteuning mogelijk met extra IP om te communiceren met de MicroSD-kaart. Dit maakt toepassingen in de praktijk mogelijk waarbij beelden moeten worden opgeslagen voor latere analyse.

Over het geheel genomen is de architectuur van het Ti180-referentieontwerp geoptimaliseerd om een compacte, goedkope, maar krachtige oplossing mogelijk te maken waarmee ontwikkelaars de BOM-kosten kunnen verlagen door middel van systeemintegratie.

Een van de belangrijkste voordelen van referentieontwerpen is dat zij kunnen worden gebruikt om de ontwikkeling van toepassingen op aangepaste hardware op gang te brengen, zodat ontwikkelaars kritieke elementen van het ontwerp kunnen overnemen en daarop kunnen voortbouwen met hun noodzakelijke aanpassingen. Dit omvat de mogelijkheid om Efinix' TinyML flow te gebruiken om vision-gebaseerde TinyML-toepassingen te implementeren die op de FPGA draaien. Dit kan zowel het parallelle karakter van FPGA-logica benutten als de mogelijkheid om gemakkelijk aangepaste instructies toe te voegen aan RISC-V-processors, waardoor binnen de FPGA-logica versnellers kunnen worden gecreëerd.

Uitvoering

Zoals besproken in deel 1, is de Efinix-architectuur uniek omdat zij gebruik maakt van eXchangeable Logic and Routing-cellen (XLR) om zowel routing- als logicafuncties te bieden. Een videosysteem zoals het referentieontwerp is een gemengd systeem dat zowel logica als routing omvat: er is uitgebreide logica nodig om de beeldverwerkingsfuncties te implementeren, en uitgebreide routing om de IP-cellen op de vereiste frequenties met elkaar te verbinden.

Het referentieontwerp gebruikt ongeveer 42% van de XLR-cellen in het apparaat, zodat er voldoende ruimte overblijft voor toevoegingen, waaronder aangepaste toepassingen zoals edge ML.

Het gebruik van het blok RAM en de digitale signaalverwerkingsblokken (DSP) is ook zeer efficiënt, met een gebruik van slechts 4 van de 640 DSP-blokken en 40% van de geheugenblokken (Afbeelding 3).

|

Afbeelding 3: Uit de toewijzing van middelen op de Efinix-architectuur blijkt dat slechts 42% van de XLR-cellen wordt gebruikt, zodat er voldoende ruimte overblijft voor extra processen. (Bron afbeelding: Adam Taylor)

Op de apparaat-IO wordt de DDR-interface voor de LPDDR4x gebruikt om het applicatiegeheugen voor de Sapphire SoC en de beeldframebuffers te leveren. Alle apparaatgebonden MIPI-bronnen worden gebruikt, samen met 50% van de faselocklussen (Afbeelding 4).

|

Afbeelding 4: Momentopname van de gebruikte interface en I/O-bronnen. (Bron afbeelding: Adam Taylor)

De general purpose I/O (GPIO) wordt gebruikt voor de I²C-communicatie, samen met verschillende interfaces die op de Sapphire SoC zijn aangesloten, waaronder NOR FLASH, USB UART en SD-kaart. De HSIO wordt gebruikt om de high-speed video-uitgang te leveren aan de ADC7511 HDMI-zender.

Een van de cruciale elementen bij het ontwerpen met FPGA's is niet alleen het implementeren en inpassen van het ontwerp in de FPGA, maar ook het kunnen plaatsen van het logische ontwerp in de FPGA en het bereiken van de vereiste timingprestaties bij het routeren.

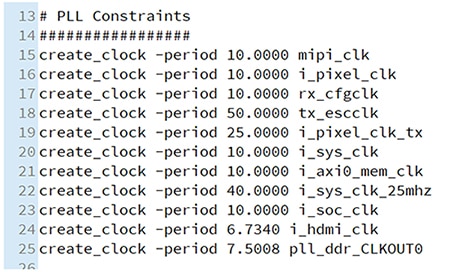

De dagen van single-clock-domain FPGA-ontwerpen zijn al lang voorbij. Er zijn verschillende klokken, die allemaal op hoge frequenties draaien in het Ti180-referentieontwerp. De uiteindelijke timingtabel toont de maximale frequenties die voor de klokken in het systeem zijn bereikt. De gevraagde timingprestaties zijn ook te zien in de beperkingen (Afbeelding 5), die een maximale klokfrequentie van 148,5 megahertz (MHz) voor de HDMI-uitgangsklok hebben.

Afbeelding 5: Klokbeperkingen voor het referentieontwerp. (Bron afbeelding: Adam Taylor)

Afbeelding 5: Klokbeperkingen voor het referentieontwerp. (Bron afbeelding: Adam Taylor)

De implementatie van de timing tegen de achtergrond van de beperkingen toont het potentieel van de XLR-structuur van de Titanium FPGA, aangezien deze de mogelijke routeringsvertraging vermindert, waardoor de prestaties van het ontwerp toenemen (Afbeelding 6).

|

Afbeelding 6: Timingimplementatie afgezet tegen de beperkingen toont het potentieel van de Titanium FPGA XLR-structuur om de mogelijke routeringsvertraging te beperken, waardoor de ontwerpprestaties toenemen. (Bron afbeelding: Adam Taylor)

Conclusie

Het Ti180 M484-referentieontwerp toont duidelijk de mogelijkheden van Efinix FPGA's en de Ti180 in het bijzonder. Het ontwerp maakt gebruik van verschillende van de unieke I/O-structuren om een complex beeldverwerkingspad te implementeren dat verschillende inkomende MIPI-streams ondersteunt. Dit beeldverwerkingssysteem werkt onder controle van een soft-core Sapphire SoC, die de noodzakelijke sequentiële verwerkingselementen van de toepassing implementeert.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.