Gebruik een efficiënte multicoreprocessor om slimmere, spraakgestuurde producten te bouwen.

Bijgedragen door De Noord-Amerikaanse redacteurs van DigiKey

2020-02-14

De vraag naar intelligentere producten is in bijna alle toepassingsgebieden alomtegenwoordig geworden doordat gebruikers vertrouwd raken met virtuele digitale assistenten zoals Amazon Alexa, Google Assistant, Apple Siri en Microsoft Cortana, en deze ook aan hen toevertrouwen. Naast het bieden van gemak, spelen deze assistenten een groeiende rol in het verbeteren van de veiligheid en beveiliging in een breed scala aan producten voor industriële systemen en toepassingen in de gezondheidszorg. Voor ontwikkelaars brengen de onderliggende ontwerpen voor deze producten echter soms tegenstrijdige eisen met zich mee voor verwerkers die in staat zijn om verbeterde prestaties, geoptimaliseerde kosten en voetafdruk en een efficiënte werking te leveren.

Dit artikel laat zien hoe ontwikkelaars een multicore processor kunnen gebruiken - in dit geval de i.MX 8M Nano van NXP- om te voldoen aan de breed uiteenlopende verwerkings- en interface-eisen van opkomende slimme producten in toepassingssegmenten variërend van slimme huis- en industriële automatisering tot medische systemen. In het bijzonder laat dit artikel zien hoe ontwikkelaars deze processor kunnen gebruiken om gemakkelijker de volgende generatie spraakgestuurde oplossingen met geavanceerde audioverwerkingsmogelijkheden te implementeren.

Hoe slimme producten zich ontwikkelen

Door de snelle opkomst van voice-assistentietechnologieën zijn gebruikers op zoek naar meer functionaliteit van slimme producten. Opkomende producten moeten niet alleen reageren op spraakcommando's, maar moeten ook meer intelligentie inbedden, met behulp van een grotere verscheidenheid aan invoergegevens van sensoren, camera's en andere producten. Het is niet genoeg dat slimme lichtschakelaars het licht aan en uit doen of dat de vaatwasser werkt op basis van spraakopdrachten. Naarmate de toepassingen groeien in geavanceerdheid, zullen de onderliggende apparaten meer uiteenlopende combinaties van sensoren, verbeterde verwerkingsmogelijkheden met behulp van kunstmatige intelligentie (AI)-methoden en 3D-graphics moeten ondersteunen.

De behoefte aan intelligentere producten gaat verder dan het verlangen naar meer gemak. In kritische toepassingsgebieden zoals industriële automatisering en gezondheidszorg kan het vermogen van een apparaat om zijn gebruikers proactief te waarschuwen voor gevaren of pathologische omstandigheden essentieel blijken. Een fabrieksarbeider die een helm draagt die de directe omgeving kan bewaken, kan gemakkelijker gevaren vermijden; een risicopatiënt die een kleine gezondheidsmonitor draagt die continu de vitale functies bewaakt, kan ruim voor een crisis de nodige ingreep krijgen.

Deze en andere slimme producten leggen specifieke ontwerpeisen op die net zo gevarieerd zijn als hun doeltoepassingen, maar de meesten delen de behoefte aan hoogwaardige verwerking, multimediamogelijkheden en een veilige werking. Voor ontwikkelaars combineren deze functionele eisen met de fundamentele behoefte aan oplossingen die in staat zijn om op te schalen om robuustere toepassingen te bedienen, terwijl ze fysiek worden afgebouwd om te voldoen aan de verwachtingen van de gebruiker voor een lagere omvang, kosten en stroomverbruik. Gebaseerd op een heterogene multicore-architectuur, voldoet de NXP i.MX 8M Nano-toepassingenprocessorfamilie aan de brede en diverse eisen van ontwerpen voor opkomende slimme producten.

Hoogwaardige kernen

De NXP i.MX 8M Nano is het nieuwste lid van de NXP i.MX 8M-processorfamilie, ontworpen om een schaalbaar multicore-verwerkingsplatform te bieden. Voor high-end videotoepassingen bieden NXP i.MX 8M flagship processors zoals de MIMX8MQ5DVAJZAB tot 4K displayresolutie met hardwarematige decodering van 4K high dynamic range (HDR)-video. Voor 1080p video bieden NXP i.MX 8M Miniprocessoren zoals de MIMX8MM6CVTKZAA 1080p hardwarematige decodeerondersteuning. Zowel de i.MX 8M als de 8M Mini serie combineren tot vier Arm® Cortex®-A53 applicatieprocessorkernen met een Arm Cortex-M4F microcontroller kern.

De NXP i.MX 8M Nano MIMX8MN6CVTIZAA-processor daarentegen combineert vier Arm Cortex-A53-kernen met een Arm Cortex-M7-kern, die de hoogste prestaties levert naast andere kernen uit de Arm Cortex-M-serie, waaronder de Cortex-M4F.

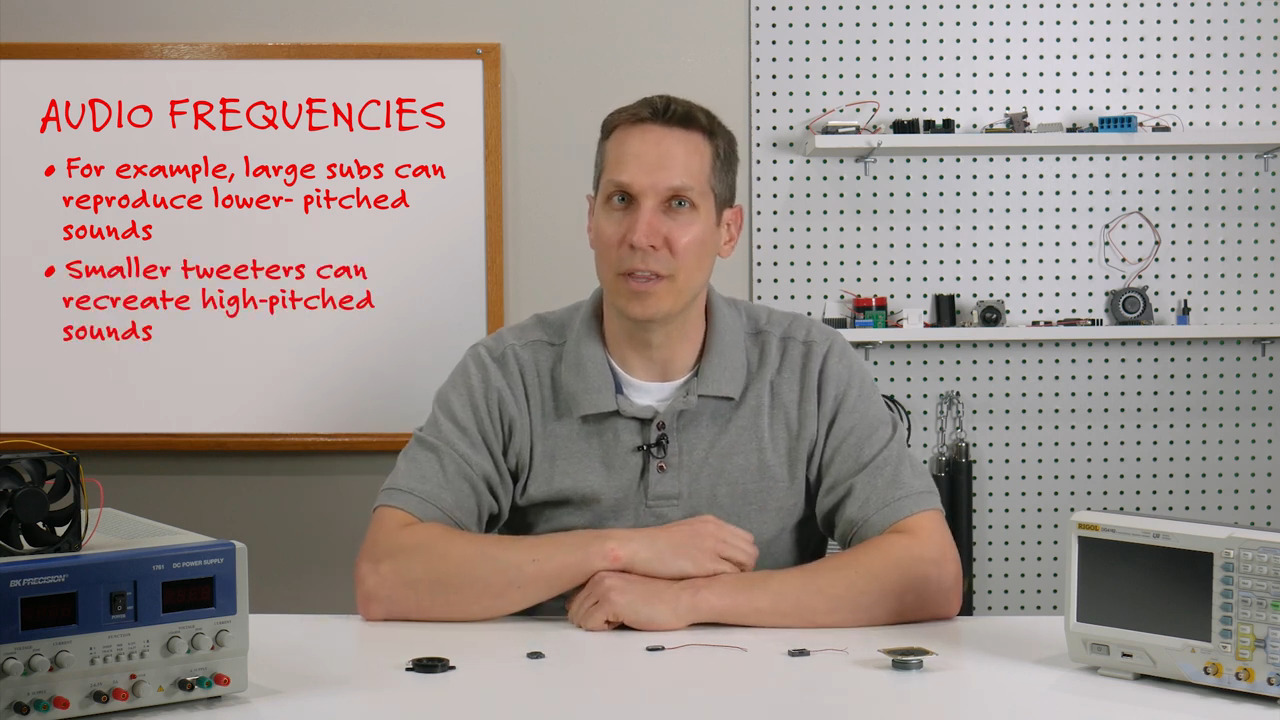

Naast hun aanvulling op de processorkernen ondersteunen i.MX 8M Nano-processoren een grote verscheidenheid aan externe geheugenapparaten en bieden ze een volledig scala aan externe perifere interfaces die doorgaans vereist zijn in consumenten- en industriële toepassingen (Afbeelding 1).

Afbeelding 1: De NXP i.MX 8M Nano-processor combineert tot vier Arm Cortex-A53 applicatieprocessoren, een Arm Cortex-M7 microcontroller, gespecialiseerde hardware-subsystemen en uitgebreide externe randapparatuur-interfaces die doorgaans worden gebruikt in consumenten- en industriële toepassingen. (Bron afbeelding: NXP)

Afbeelding 1: De NXP i.MX 8M Nano-processor combineert tot vier Arm Cortex-A53 applicatieprocessoren, een Arm Cortex-M7 microcontroller, gespecialiseerde hardware-subsystemen en uitgebreide externe randapparatuur-interfaces die doorgaans worden gebruikt in consumenten- en industriële toepassingen. (Bron afbeelding: NXP)

De verschillende beschikbare varianten van de i.MX 8M Nano-processorserie stellen ontwikkelaars in staat om eenvoudig te voldoen aan hun specifieke eisen op het gebied van kosten en prestaties. Zo integreren de high-performance leden een uitgebreid scala aan gespecialiseerde subsystemen voor beveiliging, 3D-graphics, audioverwerking en meer. Andere leden van de i.MX 8M Nano-serie bieden opties met minder Cortex-A53-kernen en "Lite"-versies met minder grafische mogelijkheden.

Alle leden van de i.MX 8M Nano-processorserie bieden echter de mogelijkheid om de combinatie van applicatieprestaties en real-time mogelijkheden te leveren die nodig zijn in opkomende slimme producten.

Ontworpen om krachtige uitvoering van toepassingssoftware te bieden, kan elke Arm Cortex-A53-toepassingsbewerkingskern werken op klokfrequenties tot 1,5 gigahertz (GHz) terwijl hij werkt vanuit een speciale niveau 1 (L1) 32 kilobyte (Kbyte) instructiecache (I-cache), 32 Kbyte gegevenscache (D-cache), en een gedeelde L2 512 Kbyte unified cache. Samen met hun geïntegreerde floating point unit (FPU) ondersteunen deze kernen Arm's Neon-technologie voor geavanceerde enkelvoudige instructie multiple data (SIMD) -bewerkingen die worden gebruikt bij digitale signaalverwerking en andere geavanceerde algoritmen in gegevensintensieve toepassingen.

Voor ingebedde systeemvereisten draait de Arm Cortex-M7 microcontroller kern op frequenties tot 750 megahertz (MHz), terwijl hij hoge prestaties levert bij de uitvoering van real-time processen die een lage latency en deterministische werking vereisen. Voor verdere snelheidsverwerking bevat de kern een geïntegreerde FPU en 256 Kbyte strak gekoppeld geheugen (TCM) dat wordt gebruikt voor instructie en data cache.

Voor complexe real-time verwerkingstaken kan de mogelijkheid om snel afzonderlijke onderbrekingsbronnen te herkennen echter net zo kritisch zijn als ruwe verwerkingskracht. In i.MX 8M Nano-processoren, een globaal interrupt controller (GIC) ingebouwd in elke Arm Cortex-A53 kern en een geneste vector interrupt controller (NVIC) in de Arm Cortex-M7 kern, maken fijne korrel interrupt behandeling van bijna 128 verschillende interrupt verzoek bronnen die overeenkomen met de kern staten, timers, perifere interface gebeurtenissen, direct-memory toegang (DMA) operaties, gespecialiseerde hardware processen, en nog veel meer mogelijk.

Heterogene meeraderige verwerking

Afzonderlijk biedt elke i.MX 8M Nano-processorkern een robuuste rekenhulpbron. De meervoudige kernen van de processor bieden samen een power-computingplatform dat goed in staat is om de tegenstrijdige eisen voor zowel realtime prestaties als de uitvoering van de applicatiesoftware te beheren, wat het ontwerp van slimme producten kan verwarren. Een slim product op basis van deze processor kan bijvoorbeeld de Cortex-M7 core gebruiken om audio streams in real time te verwerken, terwijl het algoritmes gebruikt die op een of meer Cortex-A53-kernen draaien om de resulterende gegevens te analyseren en gebruikers een 3D-grafische weergave van de resultaten te bieden.

Om dit soort gecoördineerde heterogene multicore-verwerking op betrouwbare wijze uit te voeren, vereist een multicore-systeem echter een zorgvuldige orkestratie van de verwerkingsoperaties en gegevensuitwisseling tussen de verschillende kernen, gespecialiseerde hardwareblokken en randapparatuur. In de i.MX 8M Nano-processor is deze orkestratie ingebouwd in hardwarematige mechanismen voor semaforen en berichtenverkeer die doorgaans worden gebruikt door low-level softwarediensten in multiprocessing-omgevingen.

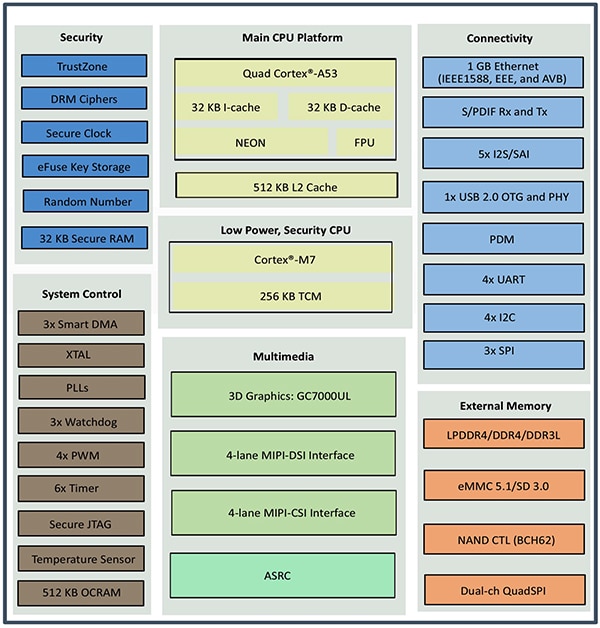

In embedded systemen strekt deze georkestreerde uitvoering zich ook uit tot hardwarebronnen zoals geheugen en randapparatuur. Voor deze taak integreert de processor een speciale resource domain controller (RDC) die is ontworpen om te zorgen voor het veilig delen van bronnen waar nodig, of betrouwbare isolatie wanneer dat nodig is. Als gevolg daarvan kan de applicatiesoftware en de realtime code van elk van de applicaties de middelen die aan hun domein zijn toegewezen, controleren terwijl ze een reeks gemeenschappelijke middelen delen (Afbeelding 2).

Afbeelding 2: Op hardware gebaseerde mechanismen in de NXP i.MX 8M Nano-processor zorgen voor isolatie van de middelen die bestemd zijn voor het Cortex-A53-toepassingsdomein of het Cortex-M7-toepassingsdomein in real-time, terwijl ze het veilig delen van middelen mogelijk maken waar nodig. (Bron afbeelding: NXP)

Afbeelding 2: Op hardware gebaseerde mechanismen in de NXP i.MX 8M Nano-processor zorgen voor isolatie van de middelen die bestemd zijn voor het Cortex-A53-toepassingsdomein of het Cortex-M7-toepassingsdomein in real-time, terwijl ze het veilig delen van middelen mogelijk maken waar nodig. (Bron afbeelding: NXP)

Gespecialiseerde ondersteuning voor slimme producten

Door alleen gebruik te maken van de i.MX 8M Nano-processor met meerdere kernen en mogelijkheden om bronnen te delen, kunnen ontwikkelaars geavanceerde toepassingen maken voor opkomende slimme producten die zijn gebouwd met voice-assistenten en 3D-afbeeldingen. Deze toepassingen krijgen een verdere prestatieverhoging terwijl ze hun software-voetafdruk verkleinen dankzij gespecialiseerde hardware-ondersteuning voor slimme producten die zijn ingebouwd in de i.MX 8M Nano-processoren.

Voor graphics biedt de geïntegreerde grafische verwerkingseenheid (GPU) van de processor 2D- en 3D- grafische versnelling en ondersteunt standaard grafische bibliotheken, waaronder Vulkan, Open Computing Language (OpenCL) en Open Graphics Library (OpenGL). Een geïntegreerde LCDIF-controller (liquid crystal display interface) ondersteunt displays met 1080p60 (1080 progressieve 60 frames per seconde).

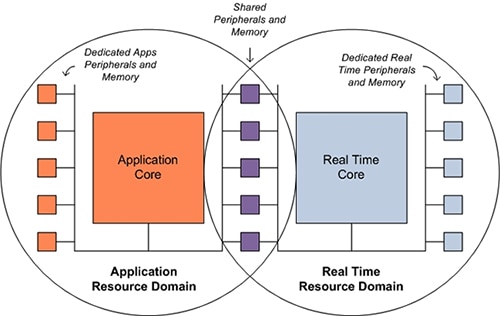

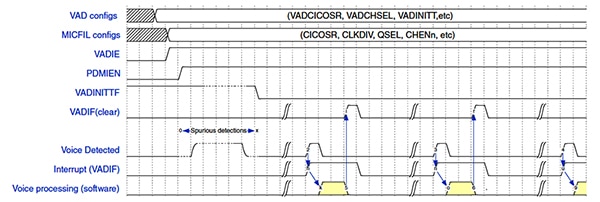

Terwijl de GPU op de chip de verwerking van de kernen weergeeft, worden door een andere set van hardware-subsystemen verschillende audioverwerkingstaken ontlast, die typisch zijn voor langzame systemen die gebaseerd zijn op conventionele processoren. Voor het verwerken van microfooningangen biedt de microfooninterface (PDM) van de processor (MICFIL) een meertrapspijpleidingen die is ontworpen om gefilterde 16-bit pulscodemodulatie (PCM)-gegevens te genereren uit de 1-bit invoer ontvangen van PDM-microfoons (Afbeelding 3) .

Afbeelding 3: Het interfacesubsysteem van de NXP i.MX 8M Nano-processor voor PDM-microfooningang combineert afzonderlijke hardwarepijpleidingen voor audiosignaalverwerking en detectie van spraakactiviteit. (Bron afbeelding: NXP)

Afbeelding 3: Het interfacesubsysteem van de NXP i.MX 8M Nano-processor voor PDM-microfooningang combineert afzonderlijke hardwarepijpleidingen voor audiosignaalverwerking en detectie van spraakactiviteit. (Bron afbeelding: NXP)

Voor een typische spraakgestuurde toepassing hoeven ontwerpers slechts een PDM-microfoon aan te sluiten op een van de acht PDM-kanalen die door de processor worden ondersteund. Binnen het PDM microfooninterface-subsysteem combineert een invoerinterface tijd gemultiplexte PDM-gegevens van een paar microfoons om een baan te vormen die linker- en rechterkanalen omvat.

In de volgende fase biedt een speciaal programmeerbaar decimatiefilter voor elk kanaal verschillende passbands, afhankelijk van de gewenste outputsnelheid en een van de zes kwaliteitskeuzes (QSEL), waaronder hoge, gemiddelde en lage kwaliteit, evenals drie extra zeer lage kwaliteitsniveaus. Bij een uitvoersnelheid van 48 kilohertz (kHz) bijvoorbeeld, stellen de zeer lage kwaliteitsmodi de filterpassband in op 10,5 Hz tot 11,25 kHz in vergelijking met een passband van 21 Hz tot 22,5 kHz voor de hoge, middelhoge en lage kwaliteitsmodi. Tot slot worden de resultaten voor elk kanaal beschikbaar gesteld in aparte first-in, first-out (FIFO)-buffers voor elk kanaal voor het genereren van interrupts, overdracht met behulp van DMA, of toegang tot de bus.

Detectie van spraakactiviteiten op basis van hardware

Parallel aan deze audiosignaalconditioneringspijplijn biedt de PDM-microfooninterface een set hardwarematige stemactiviteitsdetectoren (HWVAD's) die de gewenste microfooningangkanalen bewaken. (Opmerking: De bovenstaande afbeelding suggereert dat elke HWVAD is geassocieerd met een baan, maar de documentatie zegt kanalen, en de naam van een register, VADCHSEL, ondersteunt dat). Om de HWVAD-bewerking te ondersteunen, biedt de processor een rijke set apparaatregisters die de ontwikkelaars in staat stellen de specifieke HWVAD-configuratie te definiëren die nodig is voor hun toepassing (Tabel 1).

|

Tabel 1: NXP i.MX 8M Nano-processorregisters die gewoonlijk worden gebruikt voor het configureren van de in de PDM-microfooninterface (MICFIL) van de processor geïntegreerde hardware-spraakdetectoren. (Bron tabel: DigiKey, gebaseerd op NXP-gegevens)

Op basis van deze registerinstellingen maakt de HWVAD gebruik van ingebouwde stemdetectie-algoritmen om de stemactiviteit te identificeren. Bij detectie genereert de HWVAD een interrupt om een kern, meestal de Cortex-M7, wakker te maken voor verdere verwerking (Afbeelding 4).

Afbeelding 4: Met behulp van de door de ontwikkelaar geprogrammeerde configuratie-instellingen kunnen de NXP i.MX 8M Nano-processor-hardware-activiteitsdetectoren de processorkernen laten slapen of andere bewerkingen uitvoeren totdat er een stem wordt gedetecteerd en er verdere spraakverwerking nodig is. (Bron afbeelding: NXP)

Afbeelding 4: Met behulp van de door de ontwikkelaar geprogrammeerde configuratie-instellingen kunnen de NXP i.MX 8M Nano-processor-hardware-activiteitsdetectoren de processorkernen laten slapen of andere bewerkingen uitvoeren totdat er een stem wordt gedetecteerd en er verdere spraakverwerking nodig is. (Bron afbeelding: NXP)

In een voice-assistenttoepassing zou de kern de audiostream controleren op het juiste wekwoord. Als het wekwoord wordt gedetecteerd, zou de kern doorgaans de audiostream leveren aan de door de applicatie ondersteunde cloud-gebaseerde voice assistent-diensten.

Naast het PDM microfooninterface-subsysteem, biedt de i.MX 8M Nano processor ook vijf synchrone audio interface (SAI)-modules die een aantal standaard audioformaten ondersteunen, waaronder Inter-IC Sound (I2S), audio codec 97 (AC97), time division multiplexed (TDM) audio, en Direct Stream Digital (DSD), evenals codec of digitale signaalverwerking (DSP) data.

Om aan hun specifieke applicatie-eisen te voldoen, worden de ontwikkelaars vaak belast met de taak om audio-invoersamples om te zetten naar een andere vereiste samplefrequentie en -resolutie. In plaats van het gebruik van processorcycli om deze gemeenschappelijke taak uit te voeren, integreert de i.MX 8M Nano-processor een specifiek asynchroon voorbeeldsnelheidsconvertor (ASRC)-subsysteem.

De ASRC kan tot 32 audiokanalen tegelijkertijd verwerken en converteert automatisch bronmonsters naar de gewenste samplesnelheid (tussen 8 kHz en 384 kHz) en resolutie (IEEE single-precision floating point of vaste-puntformaat bij 16, 20, 24 of 32 bits per sample). Tijdens het proces converteert de ASRC alle invoergegevens naar een 64-bit IEEE floating point formaat om te zorgen voor een nauwkeurige opwaartse of neerwaartse conversie van audiosamplegegevens als dat nodig is om het gewenste resultaat te bereiken.

Stroombeheer met behulp van een algemene stroomregelaar

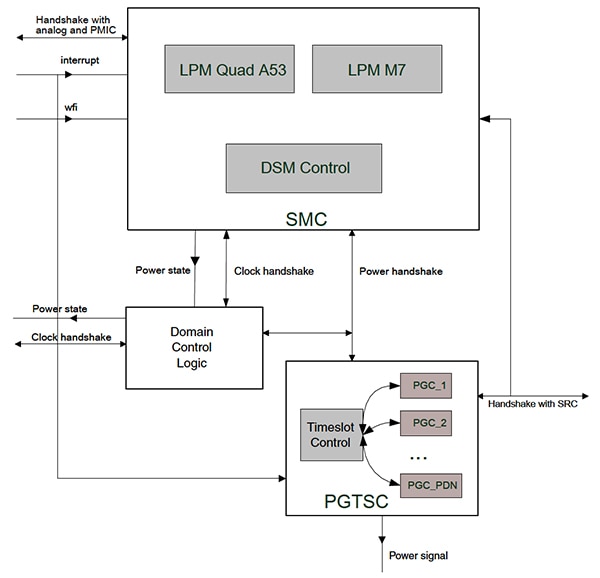

Met zijn uitgebreide integratie van processorkernen en hardware-subsystemen combineert de NXP i.MX 8M Nano-processorarchitectuur een aantal afzonderlijke krachtdomeinen en krachtmodi die in de afzonderlijke kernen en subsystemen zijn ingebouwd. Om het vermogen voor deze verzameling van kernen en gespecialiseerde blokken te beheren, bevat de i.MX 8M Nano-processor een geavanceerde algemene vermogensregelaar (GPC) die is ontworpen om meerdere vermogensbeheerfuncties te coördineren. Binnen de GPC beheert de system mode controller (SMC) de low power mode (LPM) en overall deep sleep mode (DSM) van elke core, terwijl een power gating time slot controller (PGTSC) de clock gating functies beheert die worden gebruikt om het vermogen van het systeem te verminderen door het uitschakelen van de stroom naar inactieve subsystemen (Afbeelding 5).

Afbeelding 5: Om de optimalisatie van het vermogen op systeemniveau te verbeteren, integreert de NXP i.MX 8M Nano een uitgebreide vermogenscontroller die de functies van de power gating en de in de processorkernen ingebouwde low-power modi beheert. (Bron afbeelding: NXP)

Afbeelding 5: Om de optimalisatie van het vermogen op systeemniveau te verbeteren, integreert de NXP i.MX 8M Nano een uitgebreide vermogenscontroller die de functies van de power gating en de in de processorkernen ingebouwde low-power modi beheert. (Bron afbeelding: NXP)

De GPC maakt gebruik van 20 verschillende tijdslots in de PGTSC om een van de verschillende stroomdomeinen met een klok in de processor aan te zetten of uit te schakelen, zowel voor de software als voor de hardware. Hier werkt de timeslot-controller achtereenvolgens door deze tijdslots, waarbij elke stroomop- of stroomonderbrekingsaanvraag wordt geactiveerd voordat naar het volgende slot wordt gegaan. Naast het voldoen aan specifieke eisen op het gebied van vermogensvolgorde, stelt deze aanpak ontwikkelaars in staat om de aanloopstroom te verminderen tijdens het inschakelen van het systeem, of bij het wakker worden van het systeem vanuit een laag vermogen of een diepe slaapstand.

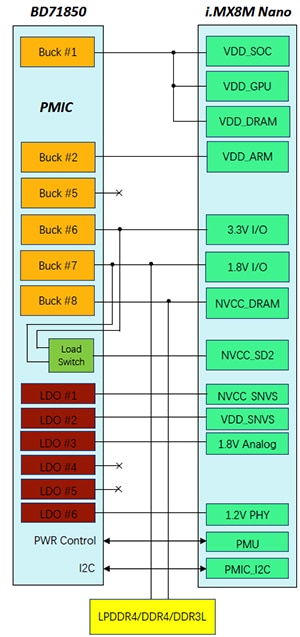

Het leveren van de meerdere krachtdomeinen van de i.MX 8M Nano-processor is eenvoudig. De ROHM Semiconductor BD71850MWV power management integrated circuit (PMIC) is speciaal ontworpen ter ondersteuning van de NXP i.MX 8M Nano-processor en biedt alle voedingsrails die de processor nodig heeft, evenals andere systeemrandapparatuur. In feite integreert de BD71850MWV PMIC zijn eigen stroomsequencer, waardoor de veilige uitvoering van het opstarten en uitschakelen verder wordt vereenvoudigd, niet alleen voor de processor, maar ook voor extern geheugen, sensoren of andere apparaten in het systeem (Afbeelding 6). Voor ontwikkelaars vereist de integratie van de BD71850MWV PMIC in een ontwerp geen extra componenten, afgezien van de gebruikelijke ontkoppelingscondensatoren (niet afgebeeld).

Afbeelding 6: De NXP iMX 8M Nano-processor heeft meerdere kernen en hardware-subsystemen nodig, maar de ROHM BD71850MWV power management integrated circuit (PMIC) biedt een kant-en-klare oplossing. (Bron afbeelding: NXP)

Afbeelding 6: De NXP iMX 8M Nano-processor heeft meerdere kernen en hardware-subsystemen nodig, maar de ROHM BD71850MWV power management integrated circuit (PMIC) biedt een kant-en-klare oplossing. (Bron afbeelding: NXP)

Ontwikkelingsondersteuning

Hoewel de hardware-interface-eisen voor i.MX 8M Nanogebaseerde ontwerpen relatief eenvoudig zijn, kunnen ontwikkelaars met NXP zelfs deze relatief eenvoudige ontwerptaak voor het evalueren van de processor of het maken van prototypes van nieuwe slimme producten vermijden. De 8MNANOD4-EVK-evaluatiekit biedt een volledig geïmplementeerde ontwikkelingskit en referentieontwerp voor de i.MX 8M Nano-processor en combineert de i.MX 8M Nano-processor en BD71850MWV PMIC met de Murata Electronics LBEE5HY1MW Wi-Fi-/Bluetooth-zendontvangmodule om een platform te bieden voor onmiddellijke evaluatie en prototype-ontwikkeling. Samen met meerdere interface-opties en bijbehorende connectoren bevat de evaluatiekit een volledige set externe geheugenapparaten, waaronder statische dynamische ram (SDRAM), NOR-flash en NAND-flash. Met behulp van de evaluatiekit kunnen ontwikkelaars verschillende bedrijfsmodi en configuraties verkennen, waaronder het opstarten van een externe flash of beveiligde boot met behulp van gesigneerde bootimages.

Wanneer ontwikkelaars klaar zijn om verder te gaan met hun eigen aangepaste softwareontwikkeling, biedt NXP-drivers, board support pakketten (BSP's), en middleware ontworpen om te werken met zijn eigen MCUXpresso geïntegreerde ontwikkelomgeving (IDE), evenals IDE's van derden. Voor het bouwen van toepassingen die zijn ontworpen om gebruik te maken van machine-leermethoden, kunnen ontwikkelaars een beroep doen op de NXP eIQ machine learning software-ontwikkelingsomgeving en i.MX-geoptimaliseerde inferentiebibliotheken zoals eIQ voor TensorFlow Lite voor Cortex-M7 gebaseerde inferentie, of NXP's poort van de Arm neurale netwerk software-ontwikkelingskit (NN SDK) voor Cortex-A53-gebaseerde inferentie.

Conclusie

Voortgestuwd door de snelle acceptatie van voice-assistentieproducten worden slimme producten van de volgende generatie geconfronteerd met groeiende verwachtingen voor niet alleen betere audio-ondersteuning, maar ook voor betere prestaties, verbeterde graphics en een energiezuinige werking. Voor ontwikkelaars vereist een effectief systeemontwerp voor deze producten echter een combinatie van krachtige uitvoering van softwaretoepassingen en realtime mogelijkheden met lage latentie die moeilijk te bereiken zijn binnen de bijbehorende omvang, kosten en stroombeperkingen Met de beschikbaarheid van een schaalbare familie van multicore processoren van NXP kunnen ontwikkelaars gemakkelijk voldoen aan de ontwerpeisen voor slimme producten in een breed scala aan applicatiesegmenten, waaronder consumenten-, industriële en medische toepassingen.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.