De co-processorarchitectuur: een ingebedde systeemarchitectuur voor snelle prototyping

2021-07-06

Editor's Note - Hoewel bekend om zijn digitale verwerkingsprestaties en verwerkingscapaciteit, biedt de co-processor architectuur de embedded systeemontwerper mogelijkheden om projectmanagement strategieën toe te passen, die zowel de ontwikkelingskosten als de time-to-market verbeteren. In dit artikel, dat specifiek gericht is op de combinatie van een discrete microcontroller (MCU) en een discrete field programmable gate array (FPGA), wordt getoond hoe deze architectuur zich leent voor een efficiënt en iteratief ontwerpproces. Gebruikmakend van onderzochte bronnen, empirische bevindingen en casestudies, worden de voordelen van deze architectuur verkend en worden voorbeeldtoepassingen gegeven. Aan het eind van dit artikel zal de ontwerper van embedded systemen beter begrijpen wanneer en hoe deze veelzijdige hardware-architectuur moet worden geïmplementeerd

Introductie

De ontwerper van ingebedde systemen bevindt zich op een kruispunt van ontwerpbeperkingen, prestatieverwachtingen, planning en budgettaire overwegingen. Zelfs de tegenstrijdigheden in de moderne modewoorden en uitdrukkingen voor projectmanagement onderstrepen het precaire karakter van deze rol: "faal snel"; "wees wendbaar"; "maak het toekomstbestendig"; en "wees ontwrichtend!". De acrobatiek die komt kijken bij zelfs maar een poging om aan deze verwachtingen te voldoen, kan schrijnend zijn, en toch zijn ze uitgesproken en worden ze nog steeds versterkt op de hele markt. Wat nodig is, is een ontwerpbenadering die een evolutionair iteratief proces mogelijk maakt, en net als bij de meeste ingebedde systemen begint dat met de hardware-architectuur.

De co-processor architectuur, een hardware architectuur die bekend staat om de combinatie van de sterke punten van zowel microcontroller unit (MCU) als field programmable gate array (FPGA) technologieën, kan de embedded ontwerper een proces bieden dat in staat is om zelfs aan de meest veeleisende eisen te voldoen, en toch de flexibiliteit biedt die nodig is om zowel bekende als onbekende uitdagingen aan te gaan. Door hardware te leveren die zich iteratief kan aanpassen, kan de ontwerper vooruitgang aantonen, kritieke mijlpalen halen en ten volle profiteren van het rapid prototyping proces.

Binnen dit proces zijn belangrijke project mijlpalen, elk met hun eigen unieke waarde toe te voegen aan de ontwikkeling inspanning. In dit artikel zal hiernaar worden verwezen met de volgende termen: De mijlpaal Digitale Signaalverwerking met de Microcontroller, de mijlpaal Systeembeheer met de Microcontroller, en de mijlpaal Productdeployment.

Aan het slot van dit artikel zal worden aangetoond dat een flexibele hardware-architectuur beter geschikt kan zijn voor het ontwerpen van moderne ingebedde systemen dan een meer rigide aanpak. Bovendien kan deze aanpak resulteren in een verbetering van zowel de projectkosten als de doorlooptijd. Argumenten, voorbeelden en case studies zullen worden gebruikt om dit standpunt te verdedigen. Door te kijken naar de waarde van elke mijlpaal binnen de ontwerpflexibiliteit die deze architectuur biedt, wordt duidelijk dat een adaptieve hardware-architectuur een krachtige drijfveer is om het ontwerp van ingebedde systemen vooruit te stuwen.

Verkenning van de sterke punten van de co-processorarchitectuur: ontwerpflexibiliteit en krachtige verwerking

Een veel voorkomende toepassing voor FPGA-ontwerpen is een rechtstreekse interface met een hogesnelheids analoog-digitaal-omzetter (ADC). Het signaal wordt gedigitaliseerd, in de FPGA ingelezen, en vervolgens worden enkele digitale signaalprocessor (DSP) algoritmen op dit signaal toegepast. Tenslotte neemt de FPGA dan beslissingen op basis van de bevindingen.

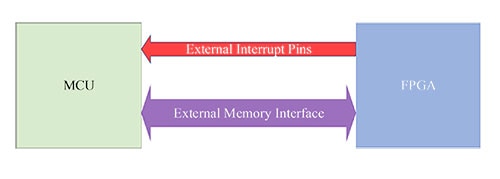

Een dergelijke toepassing zal in dit artikel als voorbeeld dienen. Voorts illustreert figuur 1 een generieke co-processorarchitectuur, waarbij de MCU en de FPGA met elkaar verbonden zijn via de externe geheugeninterface van de MCU. De FPGA wordt behandeld alsof het een stuk extern statisch random-access geheugen (SRAM) is. Signalen komen van de FPGA terug naar de MCU en dienen als hardware-interruptlijnen en statusindicatoren. Hierdoor kan de FPGA kritieke toestanden aan de MCU melden, zoals de mededeling dat een ADC-conversie gereed is, of dat een fout is opgetreden, of een andere opmerkelijke gebeurtenis heeft plaatsgevonden.

Afbeelding 1: Generiek schema van de co-processor (MCU + FPGA). (Bron afbeelding: CEPD)

Afbeelding 1: Generiek schema van de co-processor (MCU + FPGA). (Bron afbeelding: CEPD)

De sterke punten van de co-processorbenadering komen waarschijnlijk het best tot uiting in de resultaten van elk van de bovengenoemde mijlpalen. De waarde wordt beoordeeld door niet alleen de verwezenlijkingen van een taak of fase op te sommen, maar ook de mate waarin deze verwezenlijkingen het mogelijk maken deze te verwezenlijken. De antwoorden op de volgende vragen helpen bij de beoordeling van de totale waarde van de te leveren prestaties van een mijlpaal:

- Kunnen de vorderingen van andere teamleden nu sneller worden voortgezet, omdat projectafhankelijkheden en knelpunten worden weggenomen?

- Hoe maken de verwezenlijkingen van de mijlpaal verdere parallelle uitvoeringstrajecten mogelijk?

De digitale signaalverwerking met de microcontroller mijlpaal

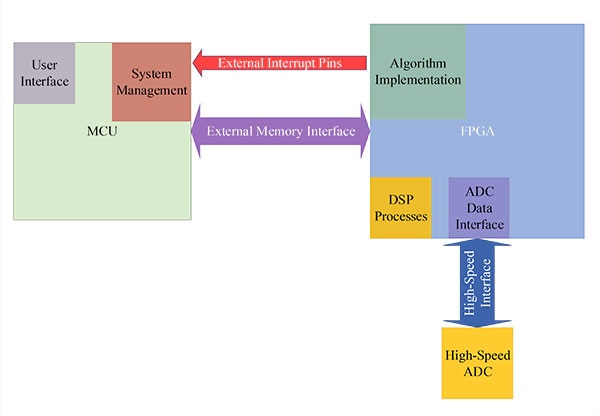

Afbeelding 2: Architectuur - digitale signaalverwerking met de microcontroller. (Bron afbeelding: CEPD)

Afbeelding 2: Architectuur - digitale signaalverwerking met de microcontroller. (Bron afbeelding: CEPD)

De eerste ontwikkelingsfase die deze hardware-architectuur mogelijk maakt, plaatst de MCU vooraan in het midden. Als alles gelijk blijft, kost de ontwikkeling van MCU's en uitvoerbare software minder middelen en tijd dan de ontwikkeling van FPGA's en hardware beschrijvende talen (HDL). Door de productontwikkeling te beginnen met de MCU als primaire processor, kunnen algoritmen sneller worden geïmplementeerd, getest en gevalideerd. Hierdoor kunnen algoritmische en logische fouten vroeg in het ontwerpproces worden ontdekt, en kunnen ook aanzienlijke delen van de signaalketen worden getest en gevalideerd.

De rol van de FPGA in deze eerste mijlpaal is te dienen als interface voor het verzamelen van gegevens tegen hoge snelheid. Zijn taak is het betrouwbaar doorvoeren van gegevens van de snelle ADC, de MCU te waarschuwen dat gegevens beschikbaar zijn, en deze gegevens te presenteren op de externe geheugeninterface van de MCU. Hoewel de implementatie van HDL-gebaseerde DSP-processen of andere algoritmen niet tot deze taak behoort, is deze toch van groot belang.

De in deze fase uitgevoerde FPGA-ontwikkeling legt de basis voor het uiteindelijke succes van het product, zowel tijdens de productontwikkelingsinspanningen als wanneer het op de markt wordt gebracht. Door alleen aandacht te besteden aan de interface op laag niveau, kan voldoende tijd worden uitgetrokken voor het testen van deze essentiële bewerkingen. Pas wanneer de FPGA deze interfacerol betrouwbaar en met vertrouwen vervult, kan deze mijlpaal met vertrouwen worden afgesloten.

De belangrijkste resultaten van deze eerste mijlpaal omvatten de volgende voordelen:

- Het volledige signaalpad - alle versterkingen, verzwakkingen en omzettingen - zal zijn getest en gevalideerd.

- De ontwikkelingstijd en -inspanning van het project zullen zijn verminderd door de algoritmen aanvankelijk in software (C/C++) uit te voeren; dit is van aanzienlijke waarde voor het management en andere belanghebbenden, die de haalbaarheid van dit project moeten inzien alvorens toekomstige ontwerpfasen goed te keuren.

- De lessen die zijn geleerd bij de implementatie van de algoritmen in C/C++ zullen rechtstreeks kunnen worden overgebracht naar HDL-implementaties - door het gebruik van software-naar-HDL-gereedschappen, bijvoorbeeld Xilinx HLS.

Het systeembeheer met de microcontroller mijlpaal

Afbeelding 3: Architectuur - systeembeheer met de microcontroller. Bron afbeelding: CEPD)

Afbeelding 3: Architectuur - systeembeheer met de microcontroller. Bron afbeelding: CEPD)

De tweede ontwikkelingsfase, die deze co-processoraanpak biedt, wordt bepaald door het verplaatsen van DSP-processen en algoritme-implementaties van de MCU naar de FPGA. De FPGA is nog steeds verantwoordelijk voor de snelle ADC-interface, maar door deze andere rollen op zich te nemen, worden de snelheid en het parallellisme die de FPGA biedt ten volle benut. Bovendien kunnen, in tegenstelling tot de MCU, meerdere instanties van de DSP-processen en algoritmekanalen worden geïmplementeerd en gelijktijdig worden uitgevoerd.

Voortbouwend op de lering die is getrokken uit de implementatie van de MCU, gaat de ontwerper met dit vertrouwen verder naar deze volgende mijlpaal. Hulpmiddelen, zoals het reeds genoemde Vivado HLS van Xilinx, zorgen voor een functionele vertaling van de uitvoerbare C/C++ code naar synthetiseerbare HDL. Nu moeten timingbeperkingen, procesparameters en andere gebruikersvoorkeuren nog worden gedefinieerd en geïmplementeerd, maar de kernfunctionaliteit wordt doorgezet en vertaald naar de FPGA-structuur.

Voor deze mijlpaal is de rol van de MCU die van een systeembeheerder. Status- en controleregisters in de FPGA worden bewaakt, bijgewerkt en gerapporteerd door de MCU. Bovendien beheert de MCU de gebruikersinterface (UI). Deze UI kan de vorm aannemen van een webserver die toegankelijk is via een ethernet- of Wi-Fi-verbinding, of het kan een industriële touchscreen-interface zijn die gebruikers toegang biedt op de plaats van gebruik. De belangrijkste conclusie die kan worden getrokken uit de nieuwe, meer verfijnde rol van de MCU is de volgende: door de rekenintensieve verwerkingstaken uit handen te nemen, kunnen zowel de MCU als de FPGA nu worden ingezet voor taken waarvoor zij zeer geschikt zijn.

De belangrijkste te leveren prestaties vormen deze mijlpaal en omvatten deze voordelen:

- Snelle, parallelle uitvoering van DSP-processen en algoritme-implementaties worden mogelijk gemaakt door de FPGA.De MCU zorgt voor een responsieve en gestroomlijnde UI en beheert de processen van het product.

- De algoritmische risico's, die eerst in de MCU zijn ontwikkeld en gevalideerd, zijn beperkt en deze risico's zijn vertaald naar synthetiseerbare HDL. Tools, zoals Vivado HLS, maken deze vertaling een eenvoudiger proces. Voorts kunnen FPGA-specifieke risico's worden beperkt door geïntegreerde simulatietools, zoals de Vivado-ontwerpsuite.

- De belanghebbenden worden niet blootgesteld aan grote risico's door de processen over te brengen naar de FPGA. Integendeel, zij krijgen te zien en te genieten van de voordelen die de snelheid en het parallellisme van de FPGA bieden. Meetbare prestatieverbeteringen worden waargenomen en de aandacht kan nu worden gericht op het fabricageklaar maken van dit ontwerp.

De mijlpaal van de productontwikkeling

Nu de rekenintensieve verwerking in de FPGA plaatsvindt, en de MCU het systeembeheer en de gebruikersinterface voor zijn rekening neemt, is het product klaar voor gebruik. In dit document wordt niet gepleit voor het omzeilen van alfa- en bèta-releases; de nadruk voor deze mijlpaal ligt echter op de mogelijkheden die de co-processorarchitectuur biedt voor de invoering van producten.

Zowel de MCU als de FPGA zijn veldupdate-apparaten. Er zijn verschillende vorderingen gemaakt om FPGA-updates net zo toegankelijk te maken als software-updates. Aangezien de FPGA zich binnen de adresseerbare geheugenruimte van de MCU bevindt, kan de MCU bovendien fungeren als toegangspunt voor het gehele systeem: zij ontvangt zowel updates voor zichzelf als voor de FPGA. Updates kunnen voorwaardelijk worden gepland, gedistribueerd en aangepast per eindgebruiker. Tenslotte kunnen gebruikers- en use-case logs worden bijgehouden en geassocieerd met specifieke build-implementaties. Aan de hand van deze gegevens kunnen de prestaties nog verder worden verfijnd en verbeterd, zelfs nadat het product in het veld is gebracht.

Misschien worden de sterke punten van deze totale actualiseerbaarheid van het systeem niet duidelijker dan bij ruimtevaarttoepassingen. Zodra een product op de markt is gebracht, moeten onderhoud en updates op afstand worden uitgevoerd. Dit kan zo eenvoudig zijn als het veranderen van logische voorwaarden, of zo ingewikkeld als het bijwerken van een communicatiemodulatieschema. De programmeerbaarheid die wordt geboden door FPGA-technologieën en de co-processorarchitectuur kunnen al deze mogelijkheden bieden, terwijl tegelijkertijd stralingbestendige componenten kunnen worden gekozen.

De laatste belangrijke conclusie die uit deze mijlpaal kan worden getrokken, is een geleidelijke kostenverlaging. Bij deze mijlpaal kunnen ook kostenverminderingen, wijzigingen van de stuklijst (BOM) en andere optimalisaties plaatsvinden. Tijdens veldinstallaties kan blijken dat het product even goed werkt met een minder dure MCU of een minder capabele FPGA. Dankzij de co-processor zitten ontwerpers van architecturen niet vast aan het gebruik van componenten waarvan de mogelijkheden de behoeften van hun toepassing te boven gaan. Mocht een component niet meer beschikbaar zijn, dan biedt de architectuur de mogelijkheid nieuwe componenten in het ontwerp te integreren. Dit is niet het geval met een single-chip, system on a chip (SoC) architectuur, of met een krachtige DSP of MCU die alle verwerking van het product voor zijn rekening probeert te nemen. De co-processor architectuur is een goede mix van mogelijkheden en flexibiliteit die de ontwerper meer keuzemogelijkheden en vrijheden geeft, zowel tijdens de ontwikkelingsfasen als bij het op de markt brengen.

Ondersteunend onderzoek en verwante case studies

Voorbeeld satellietcommunicatie

Kortom, de waarde van een co-processor is het ontlasten van de primaire verwerkingseenheid, zodat taken op hardware worden uitgevoerd, waarbij kan worden geprofiteerd van versnellingen en stroomlijning. Het voordeel van een dergelijke ontwerpkeuze is een netto toename van de rekensnelheid en -mogelijkheden, en, zoals in dit artikel wordt betoogd, een vermindering van de ontwikkelingskosten en -tijd. Een van de meest aansprekende gebieden voor deze voordelen is wellicht dat van de ruimtecommunicatiesystemen.

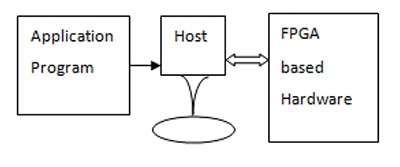

In hun publicatie, FPGA-based hardware as coprocessor, geven G. Prasad en N. Vasantha in detail aan hoe gegevensverwerking binnen een FPGA tegemoet komt aan de rekenbehoeften van satellietcommunicatiesystemen zonder de hoge eenmalige engineeringkosten (NRE) van toepassingsspecifieke geïntegreerde schakelingen (ASIC's) of de toepassingsspecifieke beperkingen van een hard-architectuur processor. Net als beschreven in de mijlpaal digitale signaalverwerking met de microcontroller, begint hun ontwerp met de toepassingsprocessor die het merendeel van de rekenintensieve algoritmen uitvoert. Vanuit dit uitgangspunt bepalen zij de belangrijkste softwaredelen die het grootste deel van de cycli van de centrale verwerkingseenheid (CPU) in beslag nemen en migreren zij deze delen naar HDL-implementatie. De grafische voorstelling lijkt sterk op wat tot dusver is gepresenteerd, maar zij hebben ervoor gekozen het toepassingsprogramma als een eigen, onafhankelijk blok weer te geven, aangezien het zowel in de host (processor) als in de op de FPGA gebaseerde hardware kan worden gerealiseerd.

Afbeelding 4: Toepassingsprogramma, hostprocessor en op FPGA's gebaseerde hardware - gebruikt in het voorbeeld van satellietcommunicatie.

Afbeelding 4: Toepassingsprogramma, hostprocessor en op FPGA's gebaseerde hardware - gebruikt in het voorbeeld van satellietcommunicatie.

Door gebruik te maken van een PCI-interface (Peripheral Component Interconnect) en de directe geheugentoegang (DMA) van de host-processor worden de prestaties van de periferie drastisch verhoogd. Dit wordt vooral waargenomen bij de verbeteringen voor het derandomiseringsproces. Wanneer dit proces werd uitgevoerd in de software van de host-processor, was er duidelijk een knelpunt in de real-time respons van het systeem. Bij overbrenging naar de FPGA werden echter de volgende voordelen geconstateerd:

- Het derandomisatieproces werd in real-time uitgevoerd zonder knelpunten te veroorzaken

- De computationele overhead van de host-processor werd aanzienlijk verminderd, en hij kon nu beter de gewenste logging-rol vervullen.

- De totale prestaties van het hele systeem werden opgeschaald.

Dit alles werd bereikt zonder de kosten die verbonden zijn aan een ASIC, en met de flexibiliteit van programmeerbare logica [5]. Satellietcommunicatie brengt aanzienlijke uitdagingen met zich mee, en met deze aanpak kan op verifieerbare wijze aan deze eisen worden voldaan, terwijl het ontwerp toch flexibel blijft.

Voorbeeld van automotive infotainment

Amusementssystemen in auto's zijn een onderscheidend kenmerk voor veeleisende consumenten. In tegenstelling tot de meeste elektronica voor auto's zijn deze apparaten zeer zichtbaar en wordt van ze verwacht dat ze een uitzonderlijke reactietijd en prestaties leveren. Ontwerpers worden echter vaak klemgezet tussen de huidige behoeften van het ontwerp en de flexibiliteit die toekomstige functies zullen vereisen. Voor dit voorbeeld zullen de implementatiebehoeften van signaalverwerking en draadloze communicatie worden gebruikt om de sterke punten van de co-processor hardware-architectuur te benadrukken.

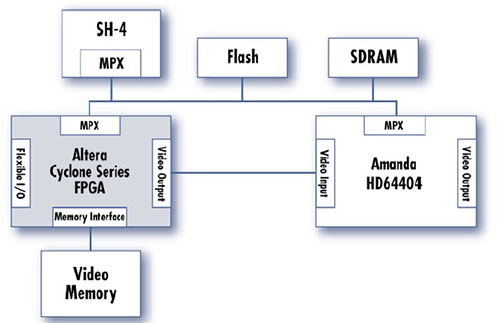

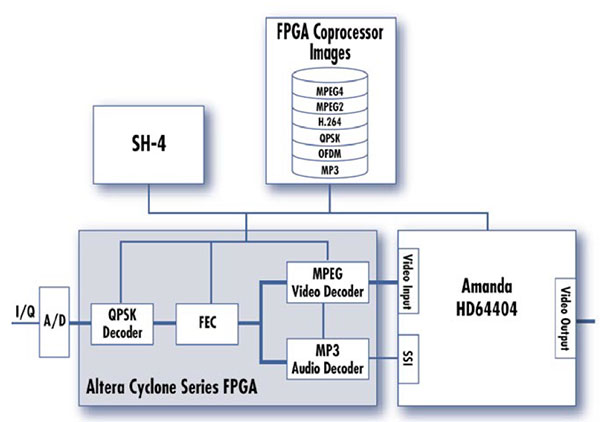

Een van de meest gebruikte entertainmentsysteemarchitecturen voor auto's werd gepubliceerd door de Delphi Delco Electronics Systems corporation. Deze architectuur maakte gebruik van een SH-4 MCU met een bijbehorende ASIC, de HD64404 Amanda-periferie van Hitachi. Deze architectuur voldeed voor meer dan 75% aan de basisbehoeften van de automarkt op het gebied van entertainment, maar was niet geschikt voor videoverwerkingstoepassingen en draadloze communicatie. Door een FPGA in deze bestaande architectuur op te nemen, kunnen nog meer flexibiliteit en mogelijkheden worden toegevoegd aan deze reeds bestaande ontwerpbenadering.

Afbeelding 5: FPGA-co-processorarchitectuurvoorbeeld voor infotainment 1.

Afbeelding 5: FPGA-co-processorarchitectuurvoorbeeld voor infotainment 1.

De architectuur van Afbeelding 5 is geschikt voor zowel videoverwerking als beheer van draadloze communicatie. Door de DSP-functies naar de FPGA te verplaatsen, kan de Amanda-processor een systeembeheerfunctie vervullen en wordt hij vrijgemaakt voor de implementatie van een draadloze communicatiestack. Aangezien zowel de Amanda als de FPGA toegang hebben tot het externe geheugen, kunnen gegevens snel worden uitgewisseld tussen de processoren en componenten van het systeem.

Afbeelding 6: FPGA-co-processorarchitectuurvoorbeeld voor infotainment 2.

Afbeelding 6: FPGA-co-processorarchitectuurvoorbeeld voor infotainment 2.

Het tweede infotainment in Afbeelding 6 laat zien dat de FPGA in staat is zowel de inkomende snelle analoge gegevens aan te pakken als de voor videotoepassingen vereiste compressie en codering uit te voeren. In feite kan al deze functionaliteit in de FPGA worden geduwd en door het gebruik van parallelle verwerking kunnen deze allemaal in real-time worden aangepakt.

Door een FPGA op te nemen in een bestaande hardwarearchitectuur kunnen de bewezen prestaties van de bestaande hardware worden gekoppeld aan flexibiliteit en toekomstbestendigheid. Zelfs binnen bestaande systemen biedt de co-processorarchitectuur opties voor ontwerpers die anders niet beschikbaar zouden zijn [6].

Voordelen van snelle prototyping

De kern van het snelle prototypingproces is dat een aanzienlijk deel van het productontwikkelingsgebied wordt bestreken door taken parallel uit te voeren, "bugs" en ontwerpproblemen snel op te sporen, en gegevens- en signaalpaden te valideren, met name die binnen het kritieke pad van een project. Wil dit proces echter werkelijk gestroomlijnde, efficiënte resultaten opleveren, dan moet er voldoende deskundigheid zijn op de vereiste projectgebieden.

Traditioneel betekent dit dat er een hardware-ingenieur, een embedded software- of DSP-ingenieur, en een HDL-ingenieur moet zijn. Nu zijn er tal van interdisciplinaire professionals, die wellicht in staat zijn meerdere rollen te vervullen; de coördinatie van deze inspanningen brengt echter nog steeds aanzienlijke projectoverhead met zich mee.

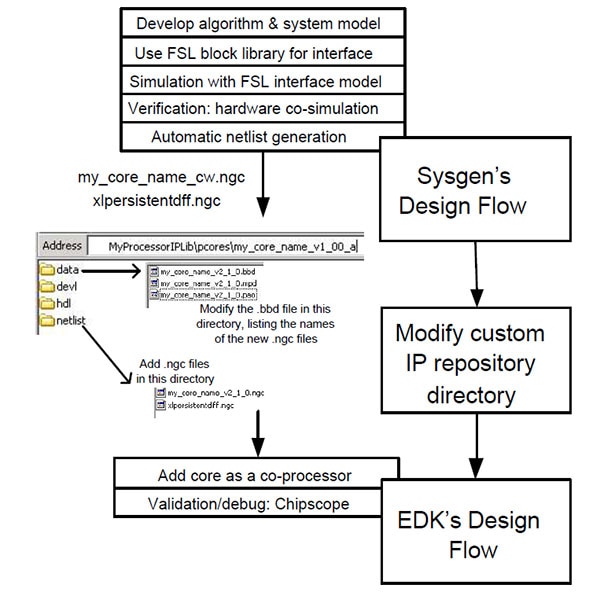

In hun artikel, Een FPGA-gebaseerd snel prototypingplatform voor wavelet coprocessoren, promoten de auteurs het idee dat het gebruik van een co-processor architectuur een enkele DSP ingenieur in staat stelt al deze rollen te vervullen, efficiënt en effectief. Voor deze studie begon het team met het ontwerpen en simuleren van de gewenste DSP-functionaliteit binnen het Simulink-hulpprogramma van MATLAB. Dit diende twee primaire functies, in die zin dat het 1) de gewenste prestaties door middel van simulatie verifieerde, en 2) diende als basislijn waarmee toekomstige ontwerpkeuzes konden worden vergeleken en waaraan kon worden gerefereerd.

Na de simulatie werden de kritische functies geïdentificeerd en verdeeld in verschillende kernen - dit zijn soft-core componenten en processoren die in een FPGA kunnen worden gesynthetiseerd. De belangrijkste stap tijdens dit werk was het definiëren van de interface tussen deze kernen en componenten en het vergelijken van de gegevensuitwisselingsprestaties met de gewenste, gesimuleerde prestaties. Dit ontwerpproces sluit nauw aan bij Xilinx's ontwerpproces voor ingebedde systemen en is samengevat in Afbeelding 7 hieronder.

Afbeelding 7: Flow van het implementatieontwerp.

Afbeelding 7: Flow van het implementatieontwerp.

Door het systeem op te delen in synthetiseerbare kernen, kan de DSP-ingenieur zich concentreren op de meest kritische aspecten van de signaalverwerkingsketen. Hij/zij hoeft geen expert te zijn in hardware of HDL om verschillende soft-core processoren of componenten in de FPGA te wijzigen, te routen of te implementeren. Zolang de ontwerper zich bewust is van de interface en de formaten van de gegevens, heeft hij volledige controle over de signaalpaden en kan hij de prestaties van het systeem verfijnen.

Empirische bevindingen - de casestudie van de discrete cosinus transform

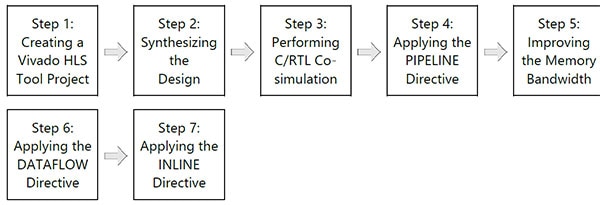

De empirische bevindingen bevestigen niet alleen de flexibiliteit die de co-processorarchitectuur de ontwerpers van ingebedde systemen biedt, maar tonen ook de mogelijkheden tot prestatieverbetering die met moderne FPGA-gereedschappen beschikbaar zijn. Verbeteringen, zoals de hieronder genoemde, zijn wellicht niet beschikbaar of hebben mogelijk minder effect op andere hardware-architecturen. De discrete cosinus transform (DCT) werd gekozen als een rekenintensief algoritme, en de overgang van een C-gebaseerde implementatie naar een HDL-gebaseerde implementatie vormde de kern van deze bevindingen. Er is gekozen voor DCT omdat dit algoritme wordt gebruikt in digitale signaalverwerking voor patroonherkenning en filtering [8]. De empirische bevindingen waren gebaseerd op een laboratoriumoefening, die door de auteur en medewerkers werd voltooid, om de Xilinx Alliance Partner certificering voor 2020 - 2021 te verkrijgen.

De volgende instrumenten en hulpmiddelen werden hierbij gebruikt:

- Vivado HLS v2019

- Het apparaat voor beoordeling en simulatie was de xczu7ev-ffvc1156-2-e

Beginnend met de C-gebaseerde implementatie, aanvaardt het DCT-algoritme twee arrays van 16-bit getallen; array "a" is de input array voor de DCT, en array "b" is de output array van de DCT. De gegevensbreedte (DW) wordt daarom gedefinieerd als 16, en het aantal elementen binnen de arrays (N) is 1024/DW, of 64. Tenslotte is de grootte van de DCT-matrix (DCT_SIZE) ingesteld op 8, hetgeen betekent dat een 8 x 8 matrix wordt gebruikt.

Volgens de premisse van dit artikel stelt de op C gebaseerde algoritme-implementatie de ontwerper in staat de functionaliteit van het algoritme snel te ontwikkelen en te valideren. Hoewel dit een belangrijke overweging is, wordt bij deze validatie aan functionaliteit een groter gewicht toegekend dan aan uitvoeringstijd. Deze weging is toegestaan, omdat de uiteindelijke implementatie van dit algoritme in een FPGA zal plaatsvinden, waar hardwareversnelling, lusafrolling en andere technieken gemakkelijk beschikbaar zijn.

Afbeelding 8: Xilinx Vivado HLS ontwerp stroom.

Afbeelding 8: Xilinx Vivado HLS ontwerp stroom.

Nadat de DCT-code in het Vivado HLS-programma als project is aangemaakt, is de volgende stap het synthetiseren van het ontwerp voor FPGA-implementatie. Het is bij deze volgende stap waar enkele van de meest impactvolle voordelen van het verplaatsen van de uitvoering van een algoritme van een MCU naar een FPGA duidelijker worden - als referentie is deze stap gelijk aan de hierboven besproken mijlpaal systeembeheer met de microcontroller.

Moderne FPGA-tools maken een reeks optimalisaties en verbeteringen mogelijk die de prestaties van complexe algoritmen sterk verbeteren. Alvorens de resultaten te analyseren, moeten enkele belangrijke termen in gedachten worden gehouden:

- Latency - Het aantal klokcycli dat nodig is om alle iteraties van de lus uit te voeren [10]

- Interval - Het aantal klokcycli voordat de volgende iteratie van een lus begint met het verwerken van gegevens [11]

- BRAM – Block Random Access Memory

- DSP48E – Digital Signal Processing Slice for the UltraScale Architecturechitectuur

- FF - Flipflop

- LUT – Look-up Table

- URAM - Unified Random-Access Memory (kan uit één enkele transistor bestaan)

|

||||||||||||||||||||||||||||||||||||||||

Tabel 1: Resultaten van de optimalisatie van de uitvoering van het FPGA-algoritme (latentie en interval).

|

Tabel 2: Resultaten van de optimalisatie van de uitvoering van het FPGA-algoritme (gebruik van hulpbronnen).

Standaard

De standaard optimalisatie-instelling komt van het ongewijzigde resultaat van het vertalen van het C-gebaseerde algoritme naar synthetiseerbare HDL. Er zijn geen optimalisaties ingeschakeld, en dit kan gebruikt worden als een prestatie referentie om de andere optimalisaties beter te begrijpen.

Binnenste lus van pijpleiding

De PIPELINE instructie instrueert Vivado HLS om de binnenste lussen af te rollen, zodat nieuwe data verwerkt kan worden terwijl bestaande data nog in de pijplijn zit. Nieuwe gegevens hoeven dus niet te wachten tot de bestaande gegevens volledig zijn voordat de verwerking kan beginnen.

Buitenste lus van pijpleiding

Door de PIPELINE-richtlijn op de buitenste lus toe te passen, worden de bewerkingen van de buitenste lus nu gepipelined. De bewerkingen van de binnenste lussen vinden nu echter gelijktijdig plaats. Zowel de latentie als de intervaltijd worden gehalveerd door dit rechtstreeks op de buitenste lus toe te passen.

Matrix-partitie

Deze instructie wijst de inhoud van de lussen toe aan arrays en vlakt zo alle geheugentoegang tot afzonderlijke elementen binnen deze arrays af. Hierdoor wordt meer RAM gebruikt, maar ook hier wordt de uitvoeringstijd van dit algoritme gehalveerd.

Dataflow

Met deze richtlijn kan de ontwerper het beoogde aantal klokcycli tussen elk van de ingangslezingen specificeren. Deze richtlijn wordt alleen ondersteund voor top-level functies. Alleen lussen en functies die op dit niveau worden blootgesteld, hebben baat bij deze richtlijn.

Inline

De INLINE directief vlakt alle lussen af, zowel binnen- als buitenlussen. Zowel rij- als kolomprocessen kunnen nu gelijktijdig worden uitgevoerd. Het aantal vereiste klokcycli wordt tot een minimum beperkt, ook al verbruikt dit meer FPGA-bronnen.

Conclusie

De architectuur van de co-processor-hardware biedt de embedded ontwerper een krachtig platform dat zijn ontwerpflexibiliteit behoudt tijdens de ontwikkeling en na de productvrijgave. Door algoritmen eerst in C of C++ te valideren, kunnen processen, gegevens- en signaalpaden en kritische functionaliteit in betrekkelijk korte tijd worden geverifieerd. Door vervolgens de processorintensieve algoritmen te vertalen naar de co-processor FPGA, kan de ontwerper profiteren van de voordelen van hardwareversnelling en een meer modulair ontwerp.

Mochten onderdelen verouderd raken of optimalisaties nodig zijn, dan kan dezelfde architectuur deze veranderingen mogelijk maken. Nieuwe MCU's en nieuwe FPGA's kunnen in het ontwerp worden ingepast, terwijl de interfaces relatief onaangeroerd kunnen blijven. Aangezien zowel de MCU als de FPGA in het veld aanpasbaar zijn, kunnen gebruikersspecifieke wijzigingen en optimalisaties bovendien in het veld en op afstand worden toegepast.

Tenslotte combineert deze architectuur de ontwikkelingssnelheid en beschikbaarheid van een MCU met de prestaties en uitbreidbaarheid van een FPGA. Met optimalisaties en prestatieverbeteringen die bij elke ontwikkelingsstap beschikbaar zijn, kan de co-processorarchitectuur voldoen aan de behoeften van zelfs de meest uitdagende eisen - zowel voor de huidige ontwerpen als daarna.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.