Maximaliseer vermogensdichtheid en prestaties in schakelende convertortoepassingen met dubbele MOSFET’s

2024-02-27

Industriële en automotive schakelende converters en motordrivers vereisen metaaloxide silicium veldeffecttransistors (MOSFET’s) die klein en efficiënt zijn en die minimale elektrische ruis genereren. Een benadering met dubbele MOSFET’s kan aan deze vereisten voldoen.

Goed ontworpen dubbele MOSFET’s, bestaande uit twee MOSFET’s in een enkele behuizing, nemen minder ruimte in op de printplaat (PCB), verminderen de parasitaire inductie en maken de noodzaak voor grote en dure koellichamen overbodig door de thermische prestaties te verbeteren. Dergelijke componenten schakelen storingsvrij bij enkele honderden kilohertz (kHz), werken stabiel over een breed temperatuurbereik en vertonen een lage lekstroom. Ontwerpers moeten echter hun werkingskarakteristieken kennen om de voordelen van deze onderdelen ten volle te benutten.

Dit artikel introduceert voorbeelden van dubbele MOSFET’s van Nexperia en laat zien hoe ontwerpers deze kunnen gebruiken om te voldoen aan de uitdagingen van robuuste, zeer efficiënte en ruimtebesparende ontwerpen. We bespreken manieren om het ontwerp van schakelingen en PCB’s te optimaliseren en bieden tips voor elektrothermische simulatie en verliesanalyse.

Meer efficiëntie bij een hoge schakelsnelheid

Dubbele MOSFET’s zijn geschikt voor veel industriële en automotive (AEC-Q101) toepassingen, waaronder DC/DC-schakelconverters, motoromvormers en regelaars voor magneetkleppen. Deze toepassingen kunnen dubbele MOSFET’s gebruiken in schakelparen en halfbrugtopologieën, naast andere configuraties.

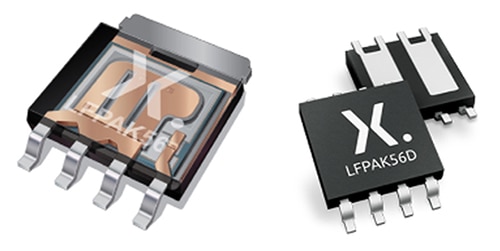

De LFPAK56D-serie van Nexperia is een opmerkelijk voorbeeld van dubbele MOSFET-componenten. Ze zijn voorzien van Nexperia’s kopercliptechnologie, die een uitzonderlijke stroomcapaciteit, lage pakketimpedantie en hoge betrouwbaarheid mogelijk maakt (afbeelding 1, rechts). Deze massief koperen clips verbeteren de warmteafvoer van het halfgeleidersubstraat via de soldeerverbindingen naar de printplaat, waarbij ongeveer 30% van de totale verwijderde warmte via de sourcepennen stroomt. De grote koperdoorsneden verlagen ook de ohmse vermogensdissipatie en dempen ringing door de parasitaire inductantie van de lijn te verminderen.

Afbeelding 1: Het LFPAK56D-pakket (rechts) integreert twee onafhankelijke MOSFET’s en maakt gebruik van koperen clipstructuren die vergelijkbaar zijn met het LFPAK56-pakket met enkele MOSFET (links). (Bron afbeelding: Nexperia)

Afbeelding 1: Het LFPAK56D-pakket (rechts) integreert twee onafhankelijke MOSFET’s en maakt gebruik van koperen clipstructuren die vergelijkbaar zijn met het LFPAK56-pakket met enkele MOSFET (links). (Bron afbeelding: Nexperia)

Zoals de meeste onderdelen die bedoeld zijn voor schakelconverters bij hoge spanning, maakt de LFPAK56D gebruik van superjunction-technologie. Dit ontwerp vermindert de parameters voor drain-source “on” weerstand (RDS(on)) en gate-drain lading (QGD), waardoor vermogensverliezen geminimaliseerd worden. Door twee MOSFET’s op hetzelfde substraat te gebruiken, wordt de drain-source-weerstand nog verder verlaagd.

De componenten in de LFPAK56D-serie zijn superjunction-MOSFET’s waardoor ze robuust zijn tegen lawines en een breed veilig werkgebied (SOA) hebben. Elk van de 100 volt MOSFET’s in het PSMN029-100HLX TrenchMOS-component heeft bijvoorbeeld een RDS(on) van 29 milliohm (mΩ), is geschikt voor 68 watt en heeft een doorlaatstroom tot 30 ampère (A).

De LFPAK56D-serie maakt ook gebruik van de SchottkyPlus-technologie van NXP om piekgedrag en lekstroom te verminderen. Bijvoorbeeld: de typische RDS(on) voor de PSMN014-40HLDX is 11,4 mΩ en de drain-source lekstroom is slechts 10 nanoampere (nA).

Om de hoge stromen van MOSFET’s volledig te benutten, moet de printplaat zo worden ontworpen dat deze grote warmte kan afvoeren en stabiele elektrische verbindingen kan garanderen. Meerlagige PCB’s met voldoende via’s en grote, dikke koperen geleiderbanen zorgen voor hoge thermische prestaties.

Thermische runaway voorkomen

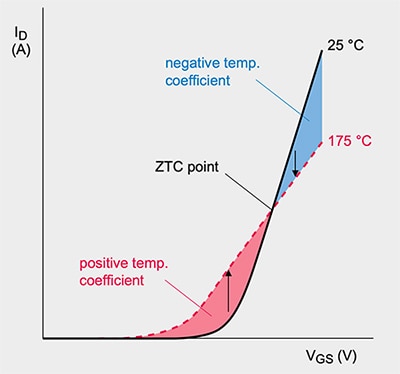

Terwijl volledig ingeschakelde vermogens-MOSFET’s thermisch stabiel zijn, is thermische runaway een risico bij een lage drainstroom (ID).In deze werkingsstaat heeft gelokaliseerde opwarming de neiging om de drempel gate-source-spanning (VGS(th)) te verlagen, wat betekent dat het component gemakkelijker inschakelt. Dit creëert een positieve terugkoppelingssituatie waarbij de extra stroom voor meer opwarming zorgt en een nog lagere VGS(th).

Afbeelding 2 toont dit effect voor een constante drain-source-spanning (VDS). Als de VGS toeneemt, is er een kritieke ID die bekend staat als de nul-temperatuurcoëfficiënt (Zero Temperature Coefficient of ZTC). Boven deze stroom is er negatieve terugkoppeling en thermische stabiliteit (blauwe zone); eronder domineert de drempelspanningsval, wat resulteert in thermisch instabiele werkingspunten die kunnen leiden tot thermische runaway (rode zone).

Afbeelding 2: Onder het ZTC-punt kan de MOSFET tot thermische runaway leiden als gevolg van een thermisch geïnduceerde VGS-daling (rode gebied). (Bron afbeelding: Nexperia)

Afbeelding 2: Onder het ZTC-punt kan de MOSFET tot thermische runaway leiden als gevolg van een thermisch geïnduceerde VGS-daling (rode gebied). (Bron afbeelding: Nexperia)

Dit effect vermindert de SOA bij lage stromen en hoge drain-source-spanningen. Dit is geen significant probleem voor snelle schakelingen met een steile dV/dt-helling. Als de schakelduur echter toeneemt, bijvoorbeeld om elektromagnetische interferentie te verminderen, wordt de thermische instabiliteit waarschijnlijker en mogelijk gevaarlijker.

Lagere schakelverliezen bij hoge frequenties

Bij het selecteren van een superjunction-MOSFET voor snel schakelende toepassingen is een lage QGD essentieel, omdat dit de schakelverliezen aanzienlijk vermindert.

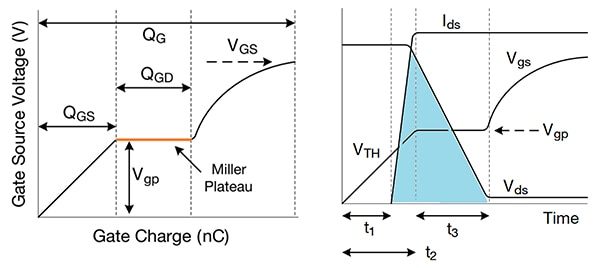

Hoog vermogensverlies treedt op tijdens het schakelen wanneer er tegelijkertijd aanzienlijke spannings- en stroomveranderingen optreden tussen de drain, gate en source. Een lage QGD resulteert in een kort Miller-plateau (afbeelding 3, links), wat leidt tot een steile schakelhelling (dVds/dt) en uiteindelijk resulteert in een lager dynamisch energieverlies tijdens het inschakelen (afbeelding 3, blauwe gebied rechts).

Afbeelding 3: Een kort Miller-plateau (links) betekent een steile schakelhelling, wat resulteert in lage dynamische verliezen (blauwe gebied rechts). Vgp is de gate-source-spanning van het Miller-plateau; VTH is de gate-drempelspanning; IDS is de drain-source-stroom. (Bron afbeelding: Vishay)

Afbeelding 3: Een kort Miller-plateau (links) betekent een steile schakelhelling, wat resulteert in lage dynamische verliezen (blauwe gebied rechts). Vgp is de gate-source-spanning van het Miller-plateau; VTH is de gate-drempelspanning; IDS is de drain-source-stroom. (Bron afbeelding: Vishay)

Lawine-energie beperken en de MOSFET beschermen

Op het uitschakelmoment van een statorspoel in een motordriver-toepassing houdt het instortende magneetveld de stroom in stand, waardoor een hoge inductiespanning over de MOSFET wordt gegenereerd, boven op de voedingsspanning (VDD). De omgekeerde doorslagspanning (VBR) van de MOSFET-hoofddiode beperkt echter deze hoge spanning. In wat bekend staat als het lawine-effect zet de MOSFET de uitstromende magnetische energie om in lawine-energie (EDS) totdat de spoelstroom tot nul daalt. Hierdoor kan het halfgeleiderkristal snel oververhit raken.

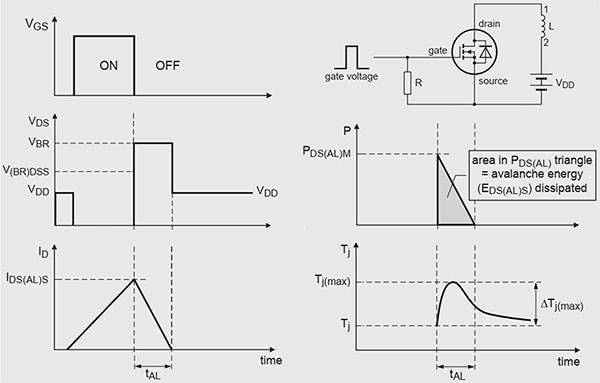

Afbeelding 4 toont een eenvoudige spoelbesturing met een MOSFET-schakelaar en de tijdsignalen vóór, tijdens (tijdvenster tAL) en na een enkele lawinegebeurtenis. Als de hoeveelheid gedissipeerde lawine-energie (EDS(AL)S) te hoog is, zal de resulterende hitte de halfgeleiderstructuur beschadigen.

Afbeelding 4: Timingsignalen van een MOSFET vóór, tijdens (tAL) en na een enkele lawinegebeurtenis. (Bron afbeelding: Nexperia)

Afbeelding 4: Timingsignalen van een MOSFET vóór, tijdens (tAL) en na een enkele lawinegebeurtenis. (Bron afbeelding: Nexperia)

De LFPAK56D-MOSFET’s zijn zeer robuust ontworpen en kunnen volgens de laboratoriumtests van Nexperia enkele miljarden lawinegebeurtenissen doorstaan zonder schade op te lopen. Gezien de maximale lawine-energie kunnen spoeldrivertrappen afzien van extra vrijloop- of klemdiodes en alleen de lawinewerking van deze MOSFET’s gebruiken.

Elektrothermische online simulatie

Om de systeemefficiëntie te verbeteren, is een eenvoudig Figure of Merit (FOM), zoals het product RDS x QGD, niet voldoende om op te vertrouwen. In plaats daarvan moeten ontwerpers een nauwkeurigere verliesanalyse uitvoeren die rekening houdt met MOSFET-verliezen als gevolg van:

- inschakelgeleiding

- inschakel- en uitschakelverliezen

- opladen en ontladen van de uitgangscapaciteit

- continuïteits- en schakelverliezen van de lichaamsdiode

- opladen en ontladen van de poortcapaciteit

Om de totale verliezen te minimaliseren, moeten ontwerpers de relatie tussen de MOSFET-parameters en de bedrijfsomgeving begrijpen. Daarom biedt Nexperia elektrothermische precisiemodellen voor MOSFET’s die elektrische en thermische prestaties combineren en alle belangrijke MOSFET-gedragingen weergeven. Ontwikkelaars kunnen de PartQuest Explore online simulator gebruiken of de modellen in SPICE- en VHDL-AMS-formaat importeren in het simulatieplatform van hun keuze.

Op het moment van schrijven zijn alleen de elektrische modellen beschikbaar voor LFPAK56D-MOSFET’s. Daarom behandelt het volgende thermische simulatievoorbeeld een ander MOSFET-type, de BUK7S1R0-40H.

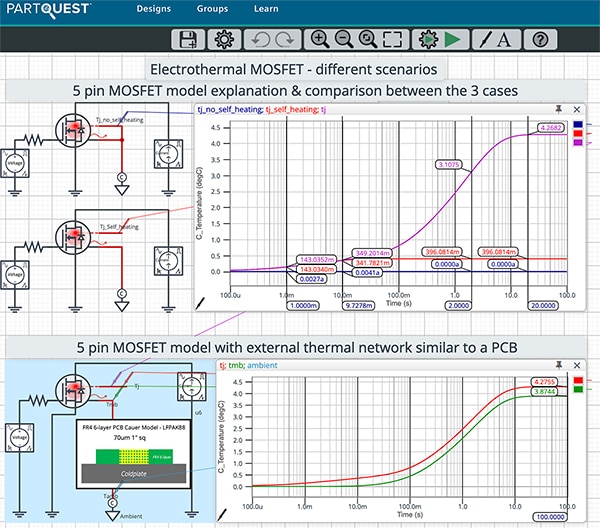

Het interactieve experiment IAN50012 Elektrothermische modellen voor vermogens-MOSFET’s simuleert drie opwarmingsscenario’s voor de BUK7S1R0-40H-MOSFET na het inschakelen van een belastingsstroom van 36,25 A. Afbeelding 5 toont de drie simulatieopstellingen aan de linkerkant.

Afbeelding 5: Elektrothermische simulatie van een MOSFET met behulp van de PartQuest Explore online simulator. (Bron afbeelding: Nexperia)

Afbeelding 5: Elektrothermische simulatie van een MOSFET met behulp van de PartQuest Explore online simulator. (Bron afbeelding: Nexperia)

In het bovenste geval, “tj_no_self_heating”, zijn de junction en mounting base direct gekoppeld aan de omgevingstemperatuur (Tamb) van 0 °C zonder thermische weerstand (Rth). In het middelste geval, “tj_self_heating”, wordt de chip gekoppeld via Rth-j en stijgt Tj met ongeveer 0,4 °C. Het onderste geval toont een mounting base (mb) gekoppeld aan de omgevingstemperatuur via de Rth_mb van een zeslaags FR4-board met een koellichaam. Tmb (groen) stijgt tot 3,9 °C en Tj (rood) stijgt tot 4,3 °C.

Conclusie

LFPAK56D-MOSFET’s met ultralage verliezen bieden een uitstekende efficiëntie en vermogensdichtheid in snel schakelende converters of motordrivers. De overwegingen bij het ontwerp van schakelingen en thermische PCB’s en de elektrothermische simulatie die hier zijn besproken, illustreren hoe ontwerpers de uitdagingen van robuuste, zeer efficiënte en ruimtebesparende ontwerpen kunnen overwinnen.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.