Basisprincipes van FPGA’s: wat zijn FPGA’s en waarom zijn ze nodig?

Bijgedragen door De Noord-Amerikaanse redacteurs van DigiKey

2019-11-14

Optimale verwerkingsoplossingen worden vaak geleverd door combinaties van RISC, CISC, grafische processors en FPGA's, door FPGA's op zichzelf, of door FPGA's die harde processorkernen als onderdeel van hun stof hebben. Er zijn echter maar weinig ontwerpers bekend met de mogelijkheden van FPGA’s, hoe die zich hebben ontwikkeld en hoe ze kunnen worden gebruikt. In dit artikel, deel 1 van een 5-delige serie, worden de fundamenten van FPGA's besproken en worden voorbeeldoplossingen van grote aanbieders geïntroduceerd. Deel 2, Deel 3, Deel 4, en Deel 5 zal zich richten op de FPGA-apparaatfamilies en ontwerphulpmiddelen die worden aangeboden van Lattice Semiconductor, Microchip, Altera, en Xilinx.

Ontwerpers zijn voortdurend op zoek naar manieren om hun systemen te optimaliseren voor een computingoplossing die voldoet aan alle toepassingsvereisten. In veel situaties vereist die optimale oplossing het gebruik van FPGA’s (field-programmable gate arrays), maar vaak zijn ontwerpers hopeloos onbekend met de mogelijkheden van deze componenten en hoe ze kunnen worden geïntegreerd.

In dit artikel worden in het kort ontwerpscenario’s beschreven die baat kunnen hebben bij het gebruik van FPGA’s. Vervolgens worden de basisprincipes behandeld en hoe FPGA’s werken, waarna een aantal interessante FPGA-oplossingen en ontwikkelingssets worden geïntroduceerd.

Waarom FPGA’s?

Er zijn tal van computertoepassingen, die elk een andere aanpak verdienen, zoals kant-en-klare microprocessors (MPU’s) en microcontrollers (MCU’s), kant-en-klare grafische verwerkingseenheden (GPU’s), FPGA’s en op maat gemaakte SoC-componenten (System-On-chip). Om te bepalen welke benadering het beste kan worden gebruikt, moeten de toepassingsvereisten en -overwegingen nauwkeurig bekeken worden.

Voor ontwerpers die bijvoorbeeld aan geavanceerde technologie werken zoals 5G-basisstations, is het belangrijk om te weten dat de onderliggende standaarden en protocollen nog steeds in ontwikkeling zijn. Dit betekent dat ontwerpers snel en efficiënt moeten kunnen reageren op veranderingen in specificaties waarop zij geen invloed hebben.

Ook moeten ze flexibel genoeg zijn om op toekomstige veranderingen in standaarden en protocollen te reageren die plaatsvinden nadat de systemen zijn geïmplementeerd. Daarnaast is het noodzakelijk om te kunnen reageren op onverwachte fouten in systeemfunctionaliteit of problemen met de systeembeveiliging, om bestaande functionaliteit te wijzigen of om nieuwe functionaliteit toe te voegen om de levensduur van het systeem te verbeteren.

Hoewel de hoogste prestaties doorgaans worden bereikt met een SoC, is deze aanpak duur en tijdrovend. Bovendien zijn alle algoritmes die in de infrastructuur van de chip worden geïmplementeerd in wezen ‘bevroren in silicium’. Deze inherente rigiditeit wordt een probleem gezien de hierboven geschetste overwegingen. Om de ‘sweet spot’ voor optimale prestaties en flexibiliteit te vinden, is een alternatieve route vereist. Die route wordt vaak bepaald door FPGA’s, combinaties van microprocessors/microcontrollers en FPGA’s of door FPGA’s die harde processorkernen als onderdeel van hun infrastructuur bevatten.

Wat zijn FPGA’s?

Dat is niet zo eenvoudig te beantwoorden omdat FPGA’s zeer veelzijdig zijn. Ook zijn er vele verschillende soorten FPGA’s, elk met een andere combinatie van mogelijkheden en functies.

Centraal bij elke FPGA staat echter de programmeerbare infrastructuur — het definiërende aspect van een FPGA als het ware — die wordt voorgesteld als een reeks programmeerbare logische blokken (Afbeelding 1a). Al deze logische blokken bevatten een verzameling elementen — waaronder een opzoektabel (LUT, look-up table), een multiplexer en een register — die allemaal naar behoefte kunnen worden geconfigureerd (geprogrammeerd) (Afbeelding 2).

Afbeelding 1: De eenvoudigste FPGA’s bevatten alleen een programmeerbare infrastructuur en configureerbare GPIO’s (a), verschillende architecturen die deze fundamentele infrastructuur invullen met SRAM-blokken, PLL’s en klokmanagers (b), DSP-blokken en SERDES-interfaces (c) en harde processorkernen en randapparaten (d). (Bron afbeelding: Max Maxfield)

Afbeelding 1: De eenvoudigste FPGA’s bevatten alleen een programmeerbare infrastructuur en configureerbare GPIO’s (a), verschillende architecturen die deze fundamentele infrastructuur invullen met SRAM-blokken, PLL’s en klokmanagers (b), DSP-blokken en SERDES-interfaces (c) en harde processorkernen en randapparaten (d). (Bron afbeelding: Max Maxfield)

Afbeelding 2: Alle programmeerbare logische blokken bevatten een verzameling elementen, waaronder een opzoektabel (LUT, look-up table), een multiplexer en een register, die naar behoefte kunnen worden geconfigureerd (geprogrammeerd). (Bron afbeelding: Max Maxfield)

Afbeelding 2: Alle programmeerbare logische blokken bevatten een verzameling elementen, waaronder een opzoektabel (LUT, look-up table), een multiplexer en een register, die naar behoefte kunnen worden geconfigureerd (geprogrammeerd). (Bron afbeelding: Max Maxfield)

Veel FPGA’s gebruiken LUT’s met 4 ingangen die kunnen worden geconfigureerd om elke gewenste logische functie met 4 ingangen te implementeren. Om de brede datapaden die in sommige toepassingen worden gebruikt beter te ondersteunen, hebben sommige FPGA’s LUT’s met 6, 7 of zelfs 8 ingangen. De LUT-uitgang wordt rechtstreeks aangesloten op een van de logische blokuitgangen en op een van de multiplexeringangen. De andere multiplexeringang is rechtstreeks aangesloten op een logische blokingang (e). De multiplexer kan worden geconfigureerd om een van deze ingangen te selecteren.

De uitgang van de multiplexer voedt de registeringang. Elk register kan worden geconfigureerd om te functioneren als edge-geactiveerde flip-flop of als een niveaugevoelige vergrendeling, hoewel het gebruik van asynchrone logica in de vorm van vergrendelingen in FPGA’s niet wordt aanbevolen. Elke registerklok (of activering) kan worden geconfigureerd als actief hoog of actief laag. Evenzo kan het actieve niveau van de set/reset-ingang(en) worden geconfigureerd.

Deze logische blokken kunnen worden gezien als ‘eilanden van programmeerbare logica’ in een ‘zee van programmeerbaar interconnect’. Dit interconnect kan zo worden geconfigureerd dat elke gewenste logische blokuitgang verbonden kan worden met elke gewenste ingang van de andere logische blokken. Op dezelfde manier kunnen de primaire ingangen aan de FPGA worden verbonden met de logische blokingangen. En de uitgangen van de logische blokken kunnen vervolgens worden gebruikt om de primaire ingangen van het component aan te sturen.

De GPIO's (general-purpose inputs/outputs) worden gepresenteerd in banken (groepen), waarbij elke bank kan worden geconfigureerd ter ondersteuning van een andere interfacestandaard, zoals LVCMOS, LVDS, LVTTL, HSTL of SSTL. Daarnaast kan de impedantie van de ingangen worden geconfigureerd evenals de variatiesnelheid van de uitgangen.

De volgende stap omhoog binnen de FPGA-infrastructuur bevat dingen zoals SRAM-blokken, block RAM (BRAM) genoemd, phase lock loops (PLL’s) en klokmanagers (Afbeelding 1b). Ook kunnen DSP-blokken (Digital Signal Processing) (DSP-slices) worden toegevoegd. Deze bevatten configureerbare multipliers en een configureerbare teller waarmee ze MAC-bewerkingen (multiply accumulate) kunnen uitvoeren (Afbeelding 1c).

Een andere veelgebruikte FPGA-functie is het gebruik van high-speed SERDES-blokken die gigabit seriële interfaces kunnen ondersteunen. Het is echter belangrijk te weten dat niet alle FPGA’s alle bovengenoemde functies ondersteunen. Verschillende FPGA’s bieden verschillende verzamelingen functies gericht op verschillende markten en toepassingen.

De programmeerbare infrastructuur in een FPGA kan worden gebruikt om elke gewenste logische functie of verzameling functies te implementeren, tot en met een of zelfs meerdere processorkernen. Deze in de programmeerbare infrastructuur geïmplementeerde kernen worden ‘zachte kernen’ genoemd. Daarentegen bevatten sommige FPGA’s — SoC FPGA’s genoemd — een of meer ‘harde processorkernen’, die rechtstreeks in het silicium worden geïmplementeerd (Afbeelding 1d). Deze harde processorkernen kunnen floating point units (FPU's) en L1/L2 cache bevatten.

Evenzo kunnen perifere interfacefuncties zoals CAN, I2C, SPI, UART en USB als zachte kernen in de programmeerbare infrastructuur worden geïmplementeerd, maar veel FPGA’s bevatten ze als harde kernen in het silicium. Communicatie tussen de processorkernen, interfacefuncties en programmeerbare infrastructuur wordt doorgaans gerealiseerd met behulp van high-speed bussen zoals AMBA en AXI.

De eerste FPGA’s, die in 1985 door Xilinx op de markt werden gebracht, hadden slechts een 8 x 8 array van programmeerbare logische blokken (geen RAM-blokken, DSP-blokken enz.). Vergelijk dat maar eens met de high-end FPGA’s van tegenwoordig die honderdduizenden logische blokken, duizenden DSP-blokken en megabits aan RAM-geheugen bevatten. In totaal kunnen ze miljarden transistors bevatten wat gelijk is aan tientallen miljoenen gelijkwaardige poorten (zoals NAND-poorten met 2 ingangen).

Andere configuratietechnologieën

De manier waarop de functies van de logische blokken en de routing van het interconnect wordt bepaald, gebeurt door middel van configuratiecellen, die kunnen worden voorgesteld als 0/1-schakelaars (uit/aan). Deze cellen worden ook gebruikt om de interfacestandaard van de GPIO, de ingangsimpedantie, de variatiesnelheid van de uitgang, enz. te configureren. Afhankelijk van de FPGA kunnen deze configuratiecellen worden geïmplementeerd met behulp van een van de volgende drie technologieën:

- Antifuse: deze configuratiecellen zijn eenmalig programmeerbaar (one-time programmable, OTP), wat betekent dat er na het programmeren van het component geen weg terug is. Deze componenten zijn doorgaans beperkt tot ruimtevaart- en beveiligingstoepassingen. En omdat ze in kleine hoeveelheden worden verkocht, hebben ze een hoog prijskaartje en zijn ze een dure ontwerpoptie.

- Flash: net als op antifuse gebaseerde configuratiecellen zijn op flash gebaseerde cellen niet-vluchtig. In tegenstelling tot antifuse-cellen kunnen flash-cellen naar behoefte opnieuw worden geprogrammeerd. Flash-configuratiecellen zijn bestand tegen straling, waardoor deze apparaten geschikt zijn voor ruimtevaarttoepassingen (zij het met aanpassingen aan hun bovenste metalliseringlagen en behuizingen).

- SRAM: in dit geval worden de configuratiegegevens opgeslagen in een extern geheugen van waaruit ze worden geladen telkens wanneer de FPGA wordt ingeschakeld (of op commando in het geval van dynamische configuratiescenario's).

Het voordeel van FPGA’s met op antifuse of flash gebaseerde configuratiecellen is dat ze ‘instant-on’ zijn en weinig stroom verbruiken. Een nadeel van deze technologieën is echter dat ze extra verwerkingsstappen nodig hebben naast het onderliggende CMOS-proces dat wordt gebruikt om de rest van de chip te creëren.

Het voordeel van FPGA’s waarvan de configuratiecellen op SRAM-technologie gebaseerd zijn, is dat ze worden vervaardigd door hetzelfde CMOS-proces als de rest van de chip en betere prestaties hebben omdat ze meestal een of twee generaties voorlopen op antifuse- en flash-technologieën. Het grootste nadeel van SRAM-configuratiecellen is dat ze meer stroom verbruiken dan antifuse- en flash-cellen (bij dezelfde technologie) en dat ze gevoelig zijn voor zogenaamde ‘single event upsets’ (SEU’s) als gevolg van straling.

Hierdoor werden op SRAM gebaseerde FPGA’s lange tijd ongeschikt geacht voor lucht- en ruimtevaarttoepassingen. Meer recentelijk worden er speciale risicobeperkende strategieën toegepast, met als gevolg dat op SRAM gebaseerde FPGA’s nu te vinden zijn op systemen zoals de Mars Curiosity Rover, samen met hun op flash gebaseerde broertjes.

Het gebruik van FPGA’s biedt flexibiliteit

FPGA’s worden voor veel verschillende toepassingen gebruikt. Ze zijn met name handig voor het implementeren van intelligente interfacefuncties, motorregeling, algoritmische versnelling en high-performance computing (HPC), beeld- en videoverwerking, machinevisie, kunstmatige intelligentie (AI), machineleren (ML), diepleren (DL), radar, bundelvorming, basisstations en communicatie.

Een goed voorbeeld is het bieden van een intelligente interface tussen apparaten die verschillende interfacestandaarden of communicatieprotocollen gebruiken. Stel dat we een bestaand systeem hebben met een toepassingsprocessor die aangesloten is op een camerasensor en een weergaveapparaat met behulp van oudere interfaces (Afbeelding 3a).

Afbeelding 3: Een FPGA kan worden gebruikt als intelligente interface tussen componenten die verschillende interfacestandaarden of communicatieprotocols gebruiken, om de levensduur van bestaande ontwerpen die zijn gebaseerd op oudere componenten te verlengen. (Bron afbeelding: Max Maxfield)

Afbeelding 3: Een FPGA kan worden gebruikt als intelligente interface tussen componenten die verschillende interfacestandaarden of communicatieprotocols gebruiken, om de levensduur van bestaande ontwerpen die zijn gebaseerd op oudere componenten te verlengen. (Bron afbeelding: Max Maxfield)

Zeg dat de makers van het systeem de camerasensor en het weergaveapparaat willen upgraden naar iets wat moderner, lichter en goedkoper is en minder stroom verbruikt. Het probleem is dat een of beide nieuwe randapparaten een moderne interfacestandaard gebruikt die niet wordt ondersteund door de oorspronkelijke applicatieprocessor (AP). Ook is het mogelijk dat ze een volledig ander communicatieprotocol ondersteunen, zoals de Mobile Industry Processor Interface (MIPI). In dit geval is het gebruik van een FPGA die meerdere I/O-standaarden ondersteunt, gekoppeld met wat zachte MIPI IP-kernen, een snelle, goedkope en risico-vrije manier van upgraden (Afbeelding 3b).

Een ander toepassingsvoorbeeld is het gebruik van FPGA’s voor rekenintensieve taken, zoals de signaalverwerking die nodig is om een radarsysteem te implementeren of voor bundelvorming in een communicatiebasisstation. Conventionele processors met een Von Neumann- of Harvard-architectuur zijn prima voor bepaalde taken, maar minder geschikt voor taken die dezelfde reeks bewerkingen herhaaldelijk moeten uitvoeren. Dit komt omdat een enkele processorkern met één enkele thread slechts één instructie tegelijk kan uitvoeren (Afbeelding 4a).

Afbeelding 4: In tegenstelling tot microprocessors waarbij slechts een enkele instructie tegelijk kan worden uitgevoerd (sequentially), kunnen meerdere functionele blokken in een FPGA diverse instructies tegelijk uitvoeren (concurrently). Ook kunnen FPGA’s massaal parallelle algoritmes implementeren. (Bron afbeelding: Max Maxfield)

Afbeelding 4: In tegenstelling tot microprocessors waarbij slechts een enkele instructie tegelijk kan worden uitgevoerd (sequentially), kunnen meerdere functionele blokken in een FPGA diverse instructies tegelijk uitvoeren (concurrently). Ook kunnen FPGA’s massaal parallelle algoritmes implementeren. (Bron afbeelding: Max Maxfield)

Meerdere functies in een FPGA kunnen echter tegelijkertijd een reeks pijplijnbewerkingen uitvoeren, waardoor een veel grotere doorvoer mogelijk is. Evenzo, in plaats van de processor dezelfde bewerking keer op keer te laten uitvoeren (zoals een extra 1000 keer op 1000 gegevensparen), kunnen deze berekeningen massaal parallel in één enkele klokcyclus in de FPGA worden uitgevoerd door 1000 tellers in de programmeerbare infrastructuur te instantiëren (Afbeelding 4b).

Wie maakt er FPGA’s?

Dit is continu in beweging. De twee belangrijkste fabrikanten van echt hoogwaardige apparaten met de hoogste capaciteit en prestaties zijn Intel (die Altera verwierf) en Xilinx.

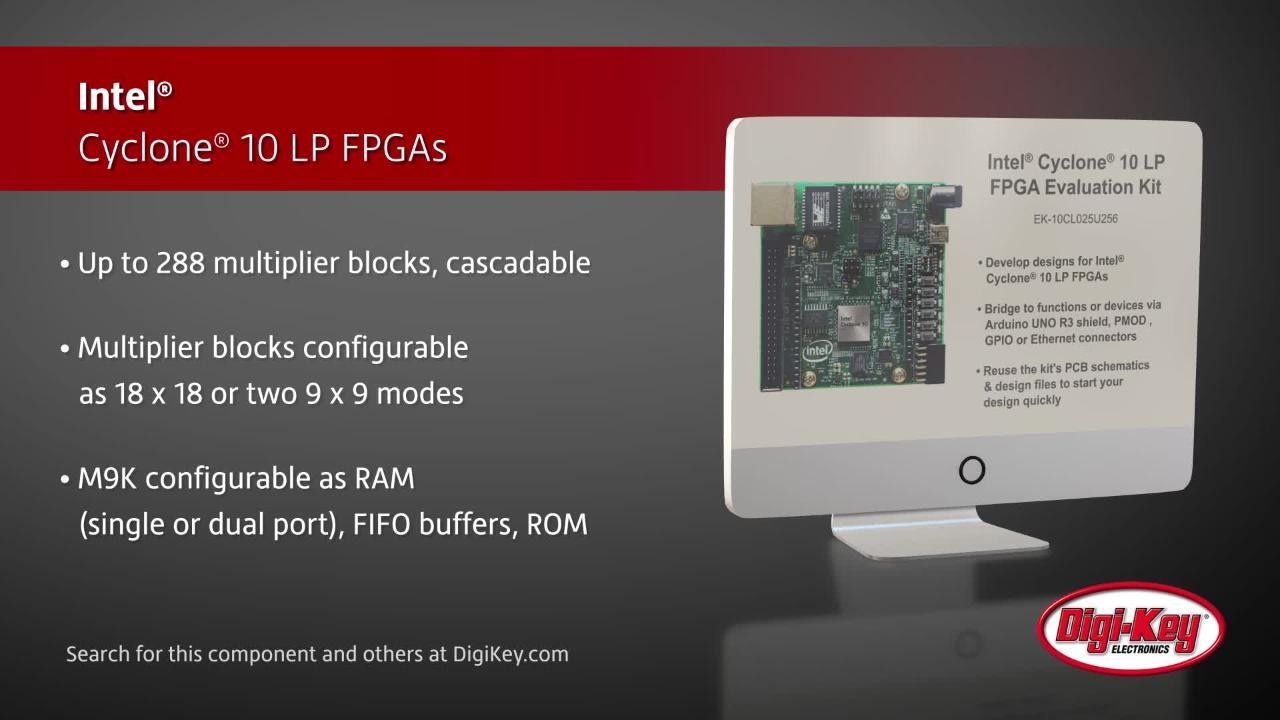

Het aanbod van Intel en Xilinx varieert van low-end FPGA’s tot en met high-end SoC FPGA’s. Een andere leverancier die zich bijna uitsluitend richt op FPGA's is Lattice Semiconductor, die zich richt op laag- en middenklasse toepassingen. Tot slot, maar niet in de laatste plaats, Microchip Technologie (via de overnames van Actel, Atmel en Microsemi) omvat nu meerdere families van kleine tot middelgrote FPGA's en low-end leden van de SoC FPGA-categorie.

Het kiezen van het beste component voor een betreffende taak kan lastig zijn, omdat er zoveel families zijn die elk verschillende resources, prestaties, capaciteiten en behuizingsstijlen bieden. Hier zijn een aantal voorbeelden: Intel-componenten, Lattice Semiconductor-componenten en Xilinx-componenten.

Ontwerpen met FPGA’s

De traditionele manier van ontwerpen met FPGA’s is door middel van een hardwarebeschrijvingstaal zoals Verilog of VHDL om het ontwerp een formele beschrijving te geven. Deze beschrijvingen kunnen eerst worden gesimuleerd om te zien of ze naar wens functioneren, waarna ze worden doorgestuurd naar een synthesetool die het configuratiebestand genereert dat wordt gebruikt om de FPGA te configureren (programmeren).

FPGA-leveranciers hebben allemaal hun eigen intern ontwikkelde toolketen of ze bieden een aangepaste versie van een tool van een gespecialiseerde leverancier. In beide gevallen zijn de tools toegankelijk via de websites van de FPGA-leverancier. Ook zijn er soms gratis of goedkopere versies van de volledige toolsuites verkrijgbaar.

Om FPGA’s toegankelijker te maken voor softwareontwikkelaars, bieden enkele FPGA-leveranciers nu high-level synthesetools (HLS) aan. Deze tools interpreteren een algoritmische beschrijving van het gewenste gedrag dat wordt vastgelegd op een hoog abstractieniveau in C, C++ of OpenCL en genereren de input voor de synthese-engine op lager niveau.

Voor beginnende ontwerpers zijn er veel ontwikkelings- en evaluatieboards beschikbaar die elk verschillende mogelijkheden en functies bieden. Drie voorbeelden zijn de DFR0600-ontwikkelingsset van DFRobot met een Zynq-7000 SoC FPGA van Xilinx, de DE10 Nano van Terasic Inc. met een Cyclone V SoC FPGA van Intel en het ICE40HX1K-STICK-EVN-evaluatieboard met een low-power iCE40 FPGA van Lattice Semiconductor.

Ontwerpers die van plan zijn een op FPGA gebaseerde PCIe-dochterbord te gebruiken om toepassingen die op een X86-moederbord draaien, te versnellen, zijn wellicht geïnteresseerd in een van de Alveo PCIe-dochterborden, ook van Xilinx.

Conclusie

Voor optimale ontwerpoplossingen wordt vaak gebruik gemaakt van FPGA’s, combinaties van processors en FPGA’s of FPGA’s die harde processorkernen als onderdeel van hun infrastructuur bevatten.

FPGA’s hebben zich de laatste jaren snel ontwikkeld en kunnen voldoen aan veel ontwerpvereisten op het gebied van flexibiliteit, verwerkingssnelheid en vermogen, waardoor ze nuttig zijn voor tal van toepassingen.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.