Inschakelen van de NVMe SSD Interface op een Xilinx ZCU102 Evaluatie Kit

Bijgedragen door De Noord-Amerikaanse redacteurs van DigiKey

2020-05-12

Overzicht

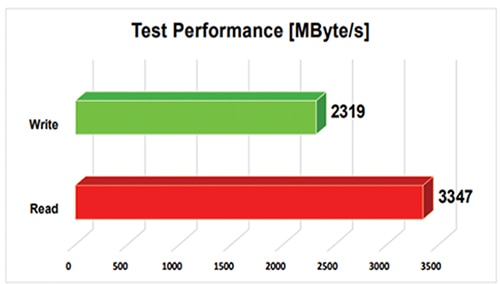

De Zynq® UltraScale+™ MPSoC familie, gebaseerd op de Xilinx®UltraScale™ MPSoC architectuur, integreert een 64-bit quad-core of dual-core ARM-gebaseerd verwerkingssysteem (PS) en Xilinx programmeerbare logica (PL) UltraScale architectuur in één enkel apparaat. Ook inbegrepen zijn on-chip geheugen, multipoort externe geheugeninterfaces, en een rijke set interfaces voor perifere connectiviteit, in het bijzonder een GTH 16,3 Gbps transceiver die de mogelijkheid biedt om een PCI Express® Gen3 opslagapparaatinterface te ondersteunen, zoals een NVMe SSD schijf. Dit artikel demonstreert de oplossing van NVMe SSD (solid state drive) interface implementatie op Xilinx's ZCU102 Evaluation Kit door gebruik te maken van Design Gateway's NVMeG3-IP Core, die in staat is om ongelooflijk snelle prestaties te bereiken: 2.319 MB/s schrijf en 3.347 MB/s leessnelheid.

Inleiding tot de Zynq® UltraScale+ MPSoC ZCU102 evaluatiekit

De ZCU102 is een algemeen evaluatiebord voor rapid-prototyping, gebaseerd op het XCZU9EG-2FFVB1156E MPSoC apparaat. De kaart bevat een snelle DDR4 SODIMM en component geheugeninterfaces, FMC uitbreidingspoorten, multi-gigabit per seconde seriële transceivers, een verscheidenheid aan perifere interfaces en FPGA logica voor door de gebruiker aangepaste ontwerpen, dit alles biedt een flexibel prototype platform.

Figuur 1: ZCU102 evaluatieset. (Afbeelding bron: Xilinx Inc.)

Figuur 1: ZCU102 evaluatieset. (Afbeelding bron: Xilinx Inc.)

De ZCU102 biedt programmeerbare logicamogelijkheden voor het creëren van state-of-the-art toepassingen zoals 5G Wireless, volgende generatie geavanceerde bestuurdersassistentiesystemen (ADAS) en Industrial Internet of Things (IIoT) oplossingen.

Hoe dan ook, voor de toepassing die externe gegevensopslag vereist met hoge prestaties en hoge betrouwbaarheid, zoals NVMe SSD drives, is de juiste oplossing nodig die gebruik maakt van de GTH Transceiver voor PCI Express® Gen3 compliance interface.

Inleiding tot NVMe SSD-opslag

NVM Express (NVMe) definieert de interface voor de hostcontroller voor toegang tot een SSD via PCI Express. NVM Express optimaliseert het proces van opdrachtverstrekking en voltooiing door slechts twee registers te gebruiken (opdrachtverstrekking en opdracht voltooiing). Anders ondersteunt NVMe parallelle werking door tot 64K opdrachten binnen één wachtrij te ondersteunen. 64K opdrachtinvoeren verbeteren de overdrachtprestaties voor zowel sequentiële als willekeurige toegang.

NVMe-schijven hebben de weg vrijgemaakt voor gegevensopslag en computers met zeer hoge snelheden. Door gebruik te maken van PCIe Express® Gen3-technologie, kunnen moderne NVMe SSD-schijven snelheden bereiken van wel 40 Gbit/s piekprestaties.

Een voorbeeld van een NVMe-opslagapparaat wordt hier getoond.

Implementatie van NVMe host controller op de ZCU102

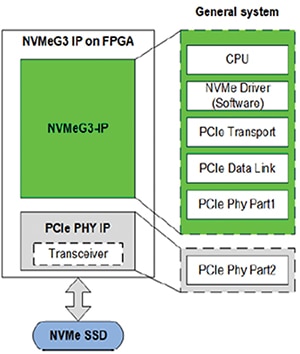

Figuur 2: NVMe-implementatie. (Afbeelding bron: Design Gateway)

Figuur 2: NVMe-implementatie. (Afbeelding bron: Design Gateway)

Gewoonlijk wordt de NVMe host geïmplementeerd door gebruik te maken van een host processor die samenwerkt met een PCIe controller voor het overbrengen van gegevens van en naar de NVMe SSD. Het NVMe-protocol is geïmplementeerd voor communicatie van het stuurprogramma met de PCIe-controller hardware CPU-randapparatuur die is verbonden via een bus met zeer hoge snelheid. Extern DDR-geheugen is nodig voor gegevensbuffering en opdrachtwachtrij om de gegevens tussen de PCIe-controller en de SSD over te dragen.

Aangezien een PCIe Gen3 Integrated Block niet beschikbaar is op een XCZU9EG-2FFVB1156E FPGA apparaat op de ZCU102, is een conventionele implementatie aanpak niet mogelijk.

Design Gateway stelt een oplossing voor door gebruik te maken van de NVMeG3-IP Core, zoals getoond in Figuur 2, om een NVMe SSD interface mogelijk te maken voor een Zynq® UltraScale+™ MPSoC apparaat waarvoor geen PCIe geïntegreerd blok beschikbaar is. De NVMe interface voor de ZCU102 maakt het mogelijk om een multi-channel RAID systeem te bouwen met zeer hoge prestaties en het laagst mogelijke FPGA resource verbruik. De NVMeG3-IP core licentie omvat het voorbeeld referentie-ontwerp dat ontwerpers helpt de ontwikkelingstijd en -kosten te verminderen.

Overzicht van NVMeG3-IP van Design Gateway

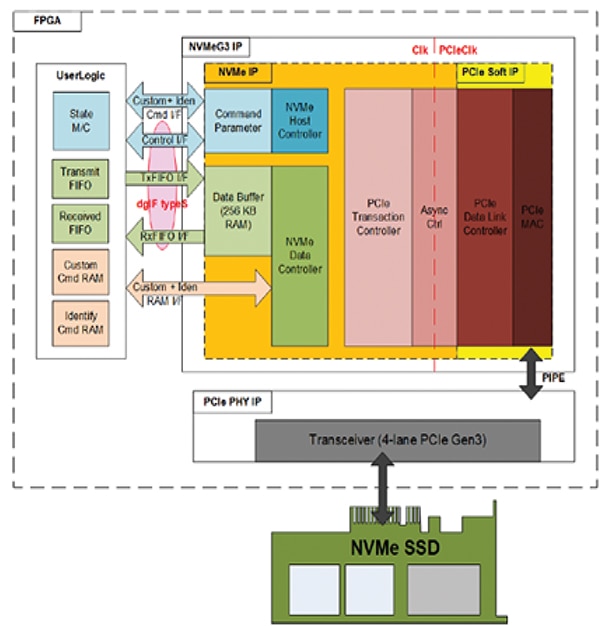

NVMe IP Core met PCIe Gen3 Soft IP (NVMeG3-IP) is ideaal voor toegang tot een NVMe SSD zonder een PCIe geïntegreerd blok, CPU, en extern geheugen. NVMeG3-IP omvat PCIe Gen3 Soft IP en 256 Kbyte geheugen. Deze oplossing wordt aanbevolen voor de toepassing die NVMe SSD-opslag vereist met ultrahoge snelheidsprestaties door gebruik te maken van een goedkope FPGA die geen PCIe geïntegreerd blok bevat.

Figuur 3: NVMeG3-IP-blokschema. (Afbeelding bron: Design Gateway)

Figuur 3: NVMeG3-IP-blokschema. (Afbeelding bron: Design Gateway)

NVMeG3-IP's kenmerken

NVMeG3-IP heeft vele kenmerken, waarvan enkele hieronder worden belicht:

- Implementeer de toepassingslaag, transactielaag, datalinklaag en sommige delen van de fysieke laag om toegang te krijgen tot de NVMe SSD zonder CPU-gebruik

- Werkt met Xilinx PCIe PHY IP geconfigureerd als een 4-baans PCIe Gen3 (128-bit bus interface)

- Inclusief 256 Kbyte RAM data buffer

- Eenvoudige gebruikersinterface via dgIF typeS

- Ondersteunt zes commando's, te weten Identificeren, Afsluiten, Schrijven, Lezen, SMART, en Spoelen (ondersteuning van extra commando's als optie)

- Ondersteund NVMe-apparaat:

- Code basisklasse:01h (massaopslag), subklassecode:08h (niet-vluchtig), programmeerinterface:02h (NVMHCI)

- MPSMIN (Minimale Geheugen Paginagrootte): 0 (4Kbyte)

- MDTS (maximale gegevensoverdrachtsgrootte): Minstens 5 (128 Kbyte) of 0 (geen beperking)

- LBA eenheid: 512 byte of 4096 byte

- De klokfrequentie van de gebruiker moet groter zijn dan of gelijk aan de PCIe-klok (250MHz voor Gen3)

- Beschikbaar referentieontwerp:

- ZCU102 met AB17-M2FMC adapterkaart

- KCU105 met adapterkaart AB18-PCIeX16/AB16-PCIeXOVR

- VCU118 met AB18-PCIeX16 adapterkaart

Design Gateway ontwikkelde de NVMeG3-IP om als NVMe host controller te werken voor toegang tot een NVMe SSD. De gebruikersinterface en standaardfuncties zijn ontworpen voor gebruiksgemak zonder dat kennis van het NVMe-protocol nodig is. De extra eigenschap van NVMeG3-IP is de ingebouwde PCIe soft IP die de Data link laag en enkele delen van de Fysieke laag van het PCIe protocol implementeert door pure logica. Dus, NVMeG3-IP kan draaien in een FPGA, die geen PCIe geïntegreerd blok heeft, door gebruik te maken van ingebouwde PCIe soft IP en Xilinx PCIe PHY IP kern. Xilinx PCIe PHY IP is een gratis beschikbare IP kern die een transceiver en een logische equalizer bevat.

NVMeG3-IP ondersteunt zes NVMe-commando's, te weten Identify, Shutdown, Write, Read, SMART en Flush. 256 Kbyte BlockRAM is geïntegreerd in de NVMeG3-IP om te fungeren als gegevensbuffer. Het systeem heeft geen CPU en extern geheugen nodig. Meer details van de NVMeG3-IP zijn beschreven in de datasheet, die kan worden gedownload van onze website.

Het gebruik van FPGA-resources op het XCZU9EG-2FFVB1156E FPGA-apparaat is weergegeven in tabel 1 hieronder.

|

Tabel 1: Voorbeeld van implementatiestatistieken voor Ultrascale/Ultrascale+-apparatuur

Implementatie en prestatieresultaat op ZCU102

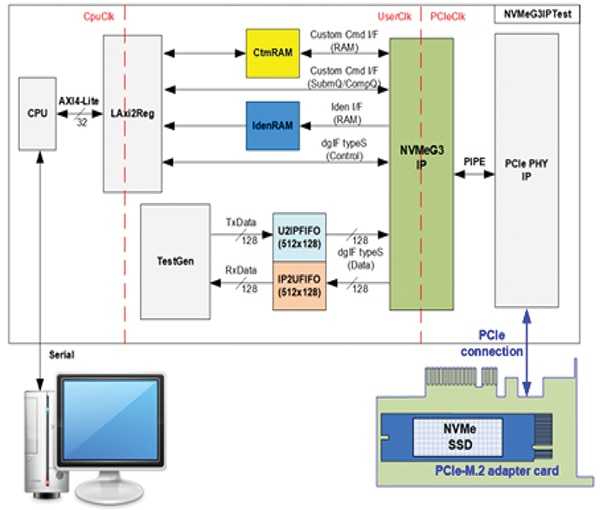

Figuur 4 toont het overzicht van het referentie-ontwerp op basis van de ZCU102 om de NVMeG3-IP werking te demonstreren. De NVMeG3IPTest module in het demosysteem bevat de volgende modules: TestGen, LAxi2Reg, CtmRAM, IdenRAM en FIFO.

Voor meer details van het NVMeG3-IP referentie-ontwerp, verwijzen wij u naar het NVMeG3-IP referentie-ontwerp document op Design Gateway's website.

Figuur 4: NVMeG3-IP referentieontwerp overzicht. (Afbeelding bron: Design Gateway)

Figuur 4: NVMeG3-IP referentieontwerp overzicht. (Afbeelding bron: Design Gateway)

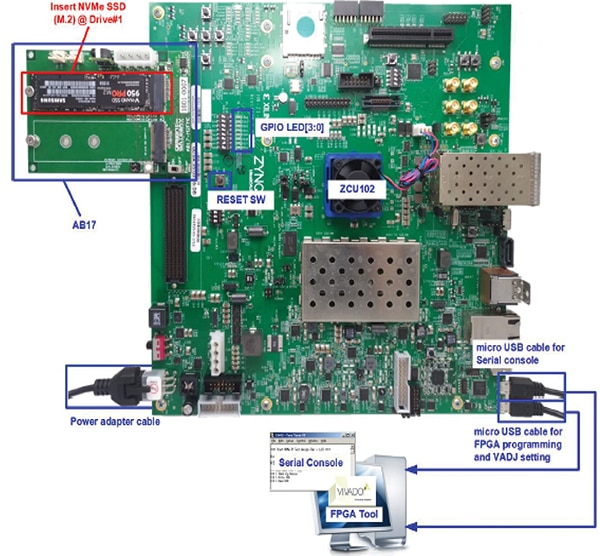

Het demo systeem is ontworpen om data te schrijven/controleren met de NVMe SSD op de ZCU102. De gebruiker bestuurt de test via een seriële console. Voor de NVMe SSD interface met de ZCU102 is een AB17-M2FMC adapter board nodig, zoals getoond in figuur 5.

Figuur 5: NVMeG3-IP demo-omgeving opgezet op ZCU102. (Afbeelding bron: Design Gateway)

Figuur 5: NVMeG3-IP demo-omgeving opgezet op ZCU102. (Afbeelding bron: Design Gateway)

Het voorbeeldtestresultaat wanneer het demosysteem op de ZCU102 wordt uitgevoerd met de 512 GB Samsung 970 Pro, wordt getoond in figuur 6.

Figuur 6: NVMe SSD lees-/schrijfprestaties op ZCU102 door gebruik van Samsung 970 PRO S. (Afbeelding bron: Design Gateway)

Figuur 6: NVMe SSD lees-/schrijfprestaties op ZCU102 door gebruik van Samsung 970 PRO S. (Afbeelding bron: Design Gateway)

Conclusie

NVMeG3-IP Core biedt een oplossing om NVMe SSD interface op de ZCU102 evaluatie kit mogelijk te maken en ook de oplossing voor Xilinx®'s Zynq® UltraScale+™ MPSoC apparaat familie waar een PCIe geïntegreerd blok niet beschikbaar is. NVMeG3-IP is ontworpen met het doel om de hoogst mogelijke prestaties te bereiken met de laagst mogelijke FPGA resource gebruik voor NVMe SSD toegang zonder dat een CPU nodig is. Het is zeer geschikt voor NVMe-opslag met hoge prestaties zonder CPU-uitvinding en kan meerdere NVMe SSD-interfaces implementeren door gebruik te maken van GTH-transceivers zonder beperkingen van het aantal beschikbare PCIe geïntegreerde blokken op het FPGA-apparaat.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.