Verwendung vertrauter Tools zur Bereitstellung von Edge-KI auf FPGAs

Zur Verfügung gestellt von Nordamerikanische Fachredakteure von DigiKey

2026-02-17

Künstliche Intelligenz (KI) am Netzwerkrand (Edge-KI) bedeutet selten nur Inferenz allein. In der Praxis sind in der Regel Highspeed-Eingabe/Ausgabe (I/O), Signalkonditionierung und Echtzeit-Steuerschleifen erforderlich, die alle gleichzeitig ausgeführt werden. Diese multifunktionalen Arbeitslasten erfordern eine enge Koordination und ein Maß an Determinismus, das die Entwickler mit herkömmlicher KI-Hardware nur schwer erreichen können.

Zwei Faktoren erschweren das Problem. Erstens entwickeln sich die KI-Modelle in einem halsbrecherischen Tempo, so dass Entwickler gezwungen sind, Plattformen einzusetzen, die schnelle Algorithmus-Updates unterstützen. Gleichzeitig bleiben viele Edge-Systeme ein Jahrzehnt oder länger im Einsatz, so dass es schwierig ist, eine langfristige Anpassungsfähigkeit zu gewährleisten. Zweitens bleibt der Weg vom trainierten Modell zum eingesetzten System fragmentiert. Datenwissenschaftler arbeiten mit PyTorch und TensorFlow, während eingebettete Teams ganz andere Toolchains verwenden, was zu Reibungsverlusten bei der Übergabe führt und die Zeit bis zur Produktion verlangsamt.

Um diese Herausforderungen zu meistern, sind Plattformen erforderlich, die KI-Verarbeitung mit hohem Durchsatz, deterministischem Verhalten, flexibler I/O und langfristiger Anpassungsfähigkeit kombinieren - und das alles bei einem begrenzten Stromverbrauch, wie er für Edge-Implementierungen typisch ist.

In diesem Artikel werden die Anwendungen und die damit verbundenen Anforderungen hervorgehoben, die die Entwickler herausfordern, neue KI-Architekturen zu entwickeln. Anschließend werden KI-fähige FPGA-Bausteine und Software-Tools von Altera vorgestellt und es wird gezeigt, wie sie eingesetzt werden können, um die Anforderungen dieser Anwendungen in einem breiten Spektrum von Performance- und Leistungspunkten zu erfüllen.

Die Entwicklung von Edge-KI erfordert architektonische Innovationen

Edge-Systeme verwenden zunehmend verschiedene KI-Techniken, klassisches maschinelles Lernen (ML) für die Erkennung von Anomalien, Faltungsneuronale Netze (CNNs) für die Wahrnehmung und Transformatoren für große Sprachmodelle (LLMs). Diese rechenintensiven Algorithmen stehen oft neben anspruchsvollen Nicht-KI-Funktionen wie Signalverarbeitung, Vernetzung und Echtzeitsteuerung.

Autonome Systeme sind ein Paradebeispiel dafür. Sie müssen oft Daten von mehreren Sensormodalitäten (z. B. Video, Audio, Radar, LiDAR und Bewegungs-/Positionsrückmeldung) aufnehmen, diese Datenströme mit hohem Durchsatz vorverarbeiten, die Ergebnisse mit ausgefeilter KI analysieren und dann hochpräzise Regelkreise verwalten - und das alles mit zuverlässigem Determinismus.

Viele ähnliche Beispiele lassen sich in den Bereichen Industrieautomation, medizinische Bildgebung, Verteidigung und Telekommunikation finden. Ein gemeinsames Problem ist, dass die konvergierenden Arbeitslasten mit traditionellen Architekturen nur schwer zu bewältigen sind.

Wie FPGAs einzigartig für Edge-KI geeignet sind

Im Gegensatz dazu lassen sich diese Anforderungen gut mit den Möglichkeiten von FPGAs verbinden. Im Kern bieten FPGAs eine konfigurierbare Logik, die Operationen wirklich parallel ausführt, wobei das Timing-Verhalten bereits zur Entwurfszeit eingebaut wird und nicht während der Laufzeit schwankt. Diese Architektur ermöglicht den Determinismus mit geringer Latenz, der für Edge-KI entscheidend ist. Die flexible Logik nutzt auch leistungsstarke I/O: FPGAs bieten in der Regel eine Fülle von Highspeed-I/O, die mit einer breiten Palette von Sensoren und Aktoren verbunden werden können und eine enge Kopplung mit der KI-Verarbeitung ermöglichen.

FPGAs enthalten auch einen verteilten internen Speicher, der die Daten in der Nähe der Logik hält, die sie verarbeitet. Dies verringert die Engpässe, die entstehen, wenn mehrere Verarbeitungsstufen um den Zugriff auf einen gemeinsamen Speicherbus konkurrieren müssen, eine häufige Einschränkung in prozessorbasierten Architekturen.

Viele FPGAs enthalten auch spezielle Hardware für die digitale Signalverarbeitung (DSP). Diese gehärteten Schaltkreise bieten eine höhere Performance und eine bessere Energieeffizienz für signalverarbeitende Aufgaben als die Allzweckstruktur. Einige FPGAs enthalten auch festverdrahtete Prozessorsysteme, auf denen Standard-Software-Stacks, einschließlich Linux, ausgeführt werden können, was die konventionelle Softwareentwicklung für Aufgaben wie Netzwerkbetrieb, Gerätemanagement und Benutzerschnittstellen ermöglicht.

Kurz gesagt, ein einziges FPGA kann Funktionen konsolidieren, die andernfalls separate I/O-Chips, KI-Beschleuniger, DSP und Steuerungsprozessoren erfordern würden. Das Ergebnis kann eine reduzierte Stückliste, ein kleinerer Platzbedarf auf der Platine und ein geringerer Stromverbrauch sein, während gleichzeitig die niedrige Latenzzeit und der Determinismus beibehalten werden, die für Edge-KI-Anwendungen erforderlich sind.

Wie das Hinzufügen von KI-Tensorblöcken neue Möglichkeiten eröffnet

Herkömmliche FPGA-DSP-Hardware eignet sich bereits gut für viele Edge-Arbeitslasten, aber KI-Inferenzen werden in der Regel durch dichte, aber niedrigpräzise Multiplikations- und Akkumulationsoperationen dominiert. Die Bausteine Agilex 3 und Agilex 5 von Altera verfügen deshalb über „Enhanced DSP“ mit KI-Tensorblöcken. Dabei handelt es sich um spezielle Hardware für Matrix-Matrix- und Vektor-Matrix-Multiplikationen, die immer wieder in KI-Rechengraphen vorkommen.

Das Herzstück dieses Ansatzes ist ein Skalarprodukt- und ein Addierer/Akkumulator-Modul (Abbildung 1). Im Tensormodus führt die festverdrahtete Dot-Engine ein 10-Element-Punktprodukt unter Verwendung von 8-Bit-Eingängen und vorgeladenen 8-Bit-Gewichten durch. Um den dynamischen Bereich zu erweitern, kann der Datenpfad auch einen „gemeinsamen Exponenten“ für die Block-Gleitkomma-Skalierung verwenden, was dem typischen Szenario entgegenkommt, in dem KI-Inferenzen einen hohen dynamischen Bereich, aber eine geringe Präzision erfordern.

Abbildung 1: Der KI-Tensorblock kann 10-Element-Punktprodukte durchführen. (Bildquelle: Altera)

Abbildung 1: Der KI-Tensorblock kann 10-Element-Punktprodukte durchführen. (Bildquelle: Altera)

Das Ergebnis des Punktprodukts besteht aus 32 Bit (Festkomma oder Gleitkomma mit einfacher Genauigkeit) und kann mit einer zusätzlichen Addierer/Akkumulator-Stufe kaskadiert werden, um größere Punktprodukte über benachbarte Blöcke zu berechnen. Jeder KI-Tensorblock enthält zwei Punktproduktspalten, die eine Vielzahl von Betriebsmodi ermöglichen.

In einem typischen Anwendungsfall wird ein Teil der verbesserten Mathematik-Hardware in ihrer traditionellen DSP-Rolle eingesetzt, z. B. zur Durchführung schneller Fourier-Transformationen (FFTs) an Radardaten. Andere werden als KI-Tensorblöcke verwendet, wie z. B. ein CNN zur Objekterkennung. Diese Flexibilität ist entscheidend für Edge-Systeme, die neben anderen rechenintensiven Funktionen auch KI verarbeiten müssen.

Eine Reihe von FPGA-Optionen für verschiedene KI-Arbeitslasten

Die Agilex-Familien bieten auch eine erhebliche Flexibilität bei der Leistungsskalierung. Die Palette reicht von effizienzorientierten Bauteilen mit Abmessungen von nur 12 mm × 12 mm bis hin zu Hochleistungsvarianten, die bis zu 152,6 Tera-Operationen pro Sekunde (TOPS) liefern, mit ähnlicher Skalierung bei den I/O- und Speicherschnittstellen.

Ein Beispiel für ein Hochleistungsbauteil ist der Agilex-5-Baustein A5ED065BB32AE4SR0, der 22,17 TOPS in einem 32 × 32 mm großen Gehäuse liefert. Ein Beispiel für ein effizienzorientiertes Bauteil ist der Agilex-3-Baustein A3CW135BM16AE6S, der 2,8 TOPS in einem 16 × 16 mm Gehäuse bietet. Die wichtigsten Spezifikationen sind in Tabelle 1 aufgeführt.

|

Tabelle 1: Einige der wichtigsten Spezifikationen der Beispiel-FPGAs Agilex 5 und Agilex 3 sind hier aufgeführt. (Quelle der Tabelle: Altera (vom Autor geändert))

Beide Familien sind als traditionelle FPGAs oder als Systems-on-Chip (SoCs) mit integrierten Arm-Prozessoren erhältlich. Die Agilex-3-SoCs verfügen über einen Dual-Core-Arm-Cortex-A55 für 800 Megahertz (MHz). Die Agilex-5-SoCs verfügen über einen asymmetrischen Cluster mit zwei 1,8 Gigahertz (GHz) Cortex-A76-Kernen neben zwei 1,5 GHz Cortex-A55-Kernen. Beide Konfigurationen unterstützen Linux und ermöglichen die konventionelle Softwareentwicklung für Netzwerke, Gerätemanagement und Benutzeroberflächen.

Einfachere Bereitstellung von Edge-KI über FPGAs

KI-Modelle werden in der Regel in Software-zentrierten Frameworks mit schnellen Iterationszyklen entwickelt, während FPGA-Implementierungen in der Vergangenheit Hardware-Entwicklungskenntnisse und längere Integrationszyklen erforderten. Die FPGA AI Suite von Altera (Abbildung 2) bietet einen direkteren Weg von einem trainierten Modell zu einsatzfähigem FPGA-Inferenz-IP (IP = Intellectual Property) unter Verwendung eines Ablaufs, der mit branchenüblichen KI-Tools kompatibel ist.

Abbildung 2: Der Arbeitsablauf der FPGA AI Suite schlägt eine Brücke zwischen Standard-KI-Frameworks und FPGA-Einsatz. (Bildquelle: Altera)

Abbildung 2: Der Arbeitsablauf der FPGA AI Suite schlägt eine Brücke zwischen Standard-KI-Frameworks und FPGA-Einsatz. (Bildquelle: Altera)

Der Arbeitsablauf lässt sich wie folgt zusammenfassen:

- Entwickeln Sie das Inferenzmodell in einem Standardrahmen wie PyTorch, TensorFlow oder ONNX.

- Verwenden Sie das OpenVINO-Toolkit, um das Modell in eine Zwischendarstellung (IR) zu konvertieren, die eine Graphdatei (.xml) und Gewichte (.bin) enthält.

- Übergeben Sie die IR-Artefakte an den FPGA-KI-Graph-Compiler, der das Modell auf die verfügbaren FPGA-Ressourcen abbildet. Zu diesen Ressourcen können ein externer Host-Prozessor, ein interner Prozessor oder eine prozessorlose Konfiguration gehören.

- Kompilieren und implementieren Sie die resultierenden Schichten mit Quartus Prime Pro Edition, wobei die Ausführung über den Laufzeit-Stack der Inferenz-Engine und die FPGA-KI-Anwendungsprogrammierschnittstellen (APIs) für Speicherbewegungen und Hardware-Scheduling verwaltet wird.

- Verwenden Sie im Rahmen des Kompilierungsprozesses den Architecture Optimizer, um Performance und Ressourcenverbrauch auszugleichen. So können Sie z. B. sicherstellen, dass die Implementierung die Zielvorgaben für den Inferenz-Durchsatz erfüllt und gleichzeitig Platz für andere FPGA-Logik lässt.

In der Praxis besteht der Wert dieses Ansatzes darin, dass er die Bereitstellung auf einem FPGA in einen Integrationsprozess und nicht in einen Aufwand für die Entwicklung eines Beschleunigers verwandelt. Datenwissenschaftler können innerhalb der etablierten Modellentwicklungs-Workflows bleiben, während FPGA- und Embedded-Teams Artefakte erhalten, die auf natürliche Weise in einen Build-and-Deploy-Zyklus passen und so eine schnellere Iteration ermöglichen, wenn sich Modelle und Anforderungen weiterentwickeln. Vorgefertigte Modelle, die über das Open Model Zoo for OpenVINO-Toolkit verfügbar sind, können die Entwicklung weiter beschleunigen.

Schneller Einstieg mit benutzerfreundlichen Entwicklungskits

Um mit der Erforschung von Edge-KI auf FPGAs zu beginnen, stehen Entwicklern mehrere Entwicklungskits zur Verfügung. Für leistungsstärkere Anwendungen ist das Atum-A5-Entwicklungskit P0775 von Terasic (Abbildung 3) eine gute Wahl. Das Kit basiert auf dem Agilex-5-Baustein A5ED065BB32AE4SR0 und bietet eine breite Palette von Schnittstellen, die sich für Systeme der Edge-Klasse eignen. Zu den wichtigsten Merkmalen gehören 8 Gigabyte DDR4, QSFP+- und 2,5-Gigabit-Ethernet-Anschlüsse (GbE), PCIe Gen 3 x4, zwei MIPI-Kameraanschlüsse und ein HDMI-Ausgang. Das Kit enthält eine kostenlose Lizenz für Quartus Prime Pro Edition.

Abbildung 3: Das Atum-A5-Entwicklungskit P0775 bietet Zugang zu leistungsstarker KI- und Bildverarbeitungsentwicklung. (Bildquelle: Terasic)

Abbildung 3: Das Atum-A5-Entwicklungskit P0775 bietet Zugang zu leistungsstarker KI- und Bildverarbeitungsentwicklung. (Bildquelle: Terasic)

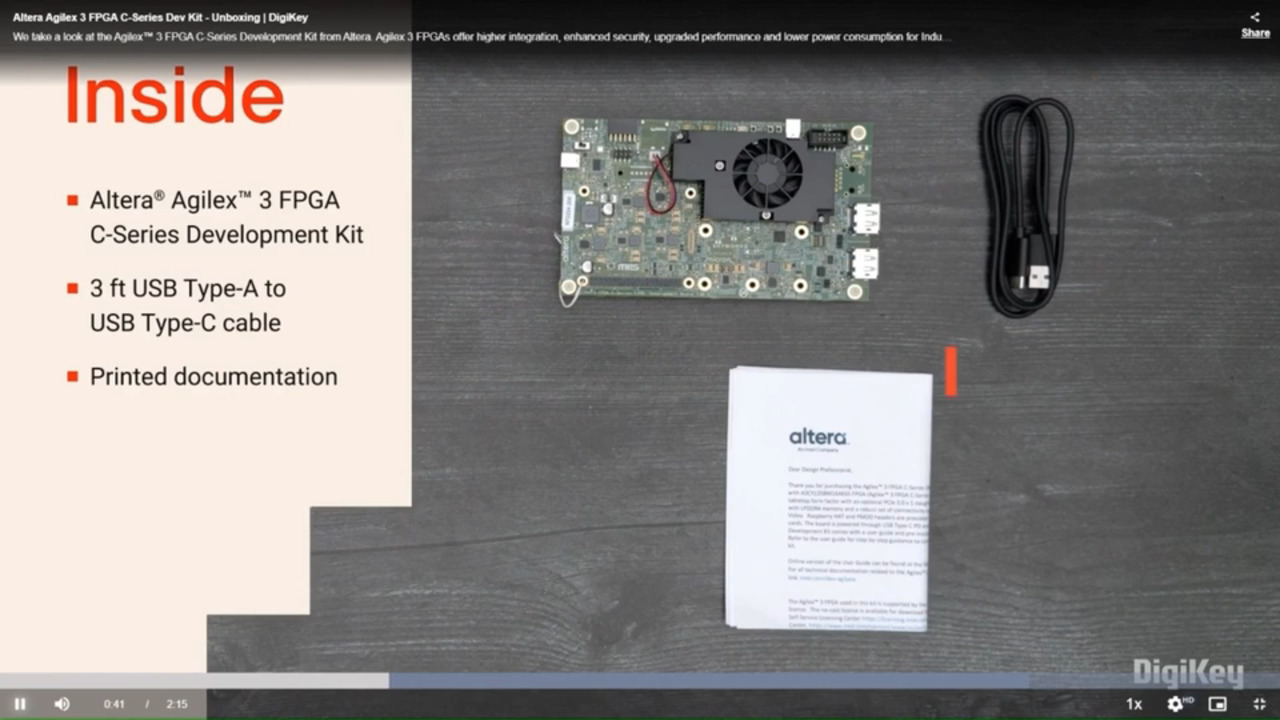

Für effizienzorientierte Anwendungen können Entwickler das Entwicklungskit DK-A3W135BM16AEA mit Agilex-3-FPGA und SoC der C-Serie verwenden (Abbildung 4). Dieses Kit basiert auf dem Agilex-3-Baustein A3CW135BM16AE6S und zeichnet sich durch kompaktes Prototyping mit ökosystemfreundlicher Erweiterung aus. Das Board bietet 4 GByte LPDDR4, GbE, DisplayPort und USB 2.0, sowie einen Raspberry-Pi-HAT-Anschluss und eine Pmod-Schnittstelle von Digilent für reibungslose Erweiterungen.

Abbildung 4: Das Entwicklungskit DK-A3W135BM16AEA mit Agilex-3-FPGA und SoC der C-Serie bietet eine kompakte Plattform für effizienzorientierte Edge-KI. (Bildquelle: Altera)

Abbildung 4: Das Entwicklungskit DK-A3W135BM16AEA mit Agilex-3-FPGA und SoC der C-Serie bietet eine kompakte Plattform für effizienzorientierte Edge-KI. (Bildquelle: Altera)

Fazit

Die Einführung von LLMs und anderen neuartigen KI-Arbeistlasten im Edge-Bereich veranlasst Entwickler dazu, neue Ansätze zu suchen. FPGAs bieten eine einzigartige Lösung, die nicht nur niedrige Latenzzeiten und deterministische Leistung bietet, sondern auch viele andere Systemfunktionen übernimmt. Mit KI-fähigen Agilex-FPGAs und der FPGA AI Suite können Entwickler schnell und einfach auf diese Fähigkeiten zugreifen und neue architektonische Möglichkeiten für hoch adaptive, langlebige Designs erschließen.

Haftungsausschluss: Die Meinungen, Überzeugungen und Standpunkte der verschiedenen Autoren und/oder Forumsteilnehmer dieser Website spiegeln nicht notwendigerweise die Meinungen, Überzeugungen und Standpunkte der DigiKey oder offiziellen Politik der DigiKey wider.